## **Embedded Coder<sup>®</sup> Support Package for Texas Instruments<sup>™</sup> C2000<sup>™</sup> Processors** Reference

# MATLAB&SIMULINK®

R2019b

#### **How to Contact MathWorks**

| Latest news:        | www.mathworks.com                    |

|---------------------|--------------------------------------|

| Sales and services: | www.mathworks.com/sales_and_services |

| User community:     | www.mathworks.com/matlabcentral      |

| Technical support:  | www.mathworks.com/support/contact_us |

| Phone:              | 508-647-7000                         |

The MathWorks, Inc. 1 Apple Hill Drive Natick. MA 01760-2098

Embedded Coder<sup>®</sup> Support Package for Texas Instruments<sup>TM</sup> C2000<sup>TM</sup> Processors Reference

© COPYRIGHT 2014-2020 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software or documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

#### **Revision History**

| October 2014   | Online only |

|----------------|-------------|

| March 2015     | Online only |

| September 2015 | Online only |

| November 2015  | Online only |

| March 2016     | Online only |

| September 2016 | Online only |

| March 2017     | Online only |

| September 2017 | Online only |

| March 2018     | Online only |

| September 2018 | Online only |

| October 2018   | Online only |

| March 2019     | Online only |

| September 2019 | Online only |

| October 2019   | Online only |

| January 2020   | Online only |

|                |             |

Revised for Version 14.2.0 (R2014b) Revised for Version 15.1.0 (R2015a) Revised for Version 15.2.0 (R2015b) Rereleased for Version 15.2.2 (R2015b) Revised for Version 16.1.0 (R2016a) Revised for Version 16.2.0 (R2016b) Revised for Version 17.1.0 (R2017a) Revised for Version 17.2.0 (R2017b) Revised for Version 18.1.0 (R2018a) Revised for Version 18.2.0 (R2018b) Revised for Version 18.2.1 (R2018b) Revised for Version 19.1.0 (R2019a) Revised for Version 19.2.0 (R2019b) Revised for Version 19.2.1 (R2019b) Revised for Version 19.2.2 (R2019b)

## Contents

#### **Configuration Parameters**

| Hardware Implementation Pane: Texas Instruments C2000 |            |

|-------------------------------------------------------|------------|

| Processors                                            | 1-2<br>1-2 |

| C28x-Scheduler Options                                | 1-37       |

| C28x-Build Options                                    | 1-38       |

| C28x-Clocking                                         | 1-42       |

| C28x-ADC/C28x-ADC_A/C28x-ADC#                         | 1-46       |

| С28х-СОМР                                             | 1-49       |

| C28x-DAC                                              | 1-50       |

| C28x-eCAN_A, C28x-eCAN_B                              | 1-51       |

| С28х-еСАР                                             | 1-53       |

| С28х-еРWM                                             | 1-54       |

| C28x-I2C                                              | 1-57       |

| C28x-SCI_A, C28x-SCI_B, C28x-SCI_C, C28x_SCI_D        | 1-63       |

| C28x-SPI_A, C28x-SPI_B, C28x-SPI_C, C28x-SPI_D        | 1-66       |

| C28x-eQEP                                             | 1-68       |

| C28x-Watchdog                                         | 1-69       |

1

| C28x-GPIO           | 1-71  |

|---------------------|-------|

| C28x-DMA_ch#        | 1-76  |

| C28x-EMIF           | 1-84  |

| C28x-LIN            | 1-91  |

| External Interrupt  | 1-97  |

| External Mode       | 1-98  |

| Execution profiling | 1-99  |

| SD Card Logging     | 1-100 |

### Blocks — Alphabetical List

## 2

#### Appendix

## 3

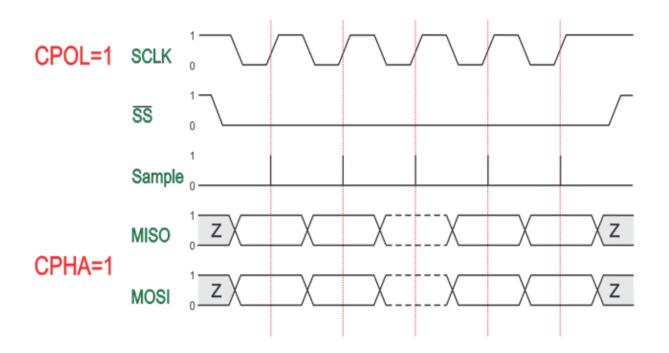

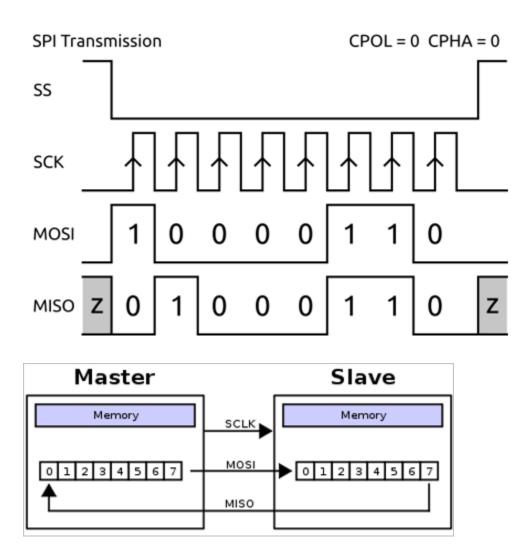

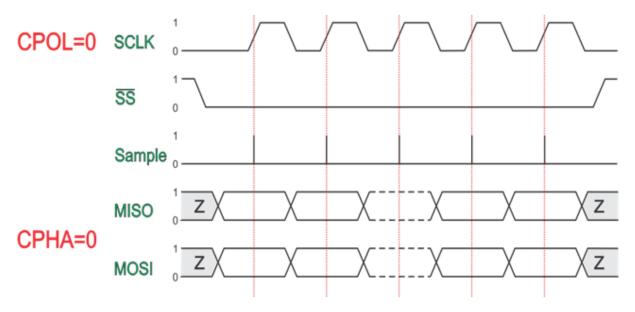

| Support SPI Communication | • |

|---------------------------|---|

| SPI Lines                 |   |

| Data Transmission         |   |

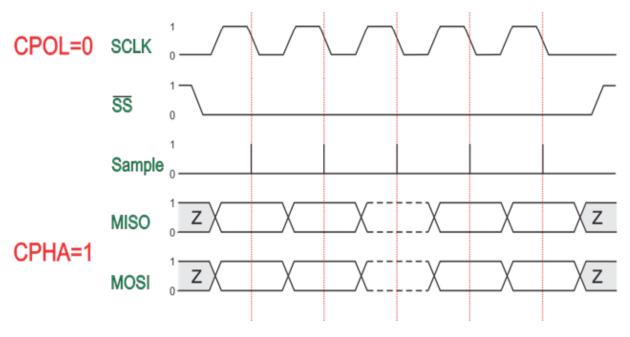

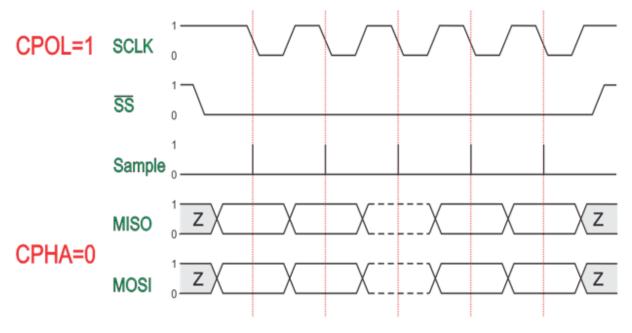

| SPI Transfer Modes        |   |

## **Configuration Parameters**

#### Hardware Implementation Pane: Texas Instruments C2000 Processors

To configure hardware parameters for Texas Instruments C2000 processors:

- **1** In the Simulink<sup>®</sup> Editor, select **Simulation > Model Configuration Parameters**.

- 2 In the Configuration Parameter dialog box, click **Hardware Implementation**.

- **3** Set the **Hardware board** parameter to your C2000 processor.

- **4** The parameter values under **Hardware board settings** are automatically populated to their default values.

You can optionally adjust these parameters for your particular use case.

5 Click Apply.

**Note** In the **Hardware board** drop-down list, some processors have multiple options. Select the generic option for controlCARDs and custom boards, and select the LaunchPad option for LaunchPads. For example, select **TI Delfino F2837xS** as the generic option, and select **TI Delfino F28377S Launchpad** as the LaunchPad option. Based on your selection, the default values for clock settings, pin selection, and memory mapping change.

#### **Hardware Board Settings**

For each hardware board you select, you can configure the board parameters according to your requirements.

#### **Scheduler Options**

| Parameter | Description                                                                  | Default Value |

|-----------|------------------------------------------------------------------------------|---------------|

|           | Set the static priority of the<br>base rate task in the<br>operating system. | Timer 0       |

#### **Build Options**

| Parameter                                                                                                               | Description                                                                                                   | Default Value        |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------|

| Build action on page 1-38                                                                                               | Define how Embedded<br>Coder responds when you<br>build your model.                                           | Build, load, and run |

| Device name on page 1-38                                                                                                | Select your device from the selected processor family.                                                        |                      |

| Enable TMU on page 1-38                                                                                                 | Enables support for<br>Trigonometric Math Unit<br>(TMU)                                                       | enabled              |

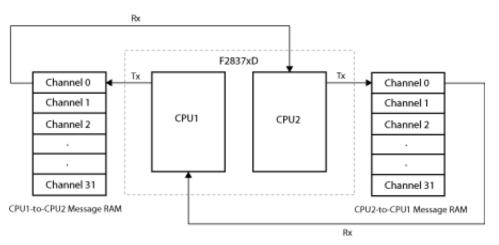

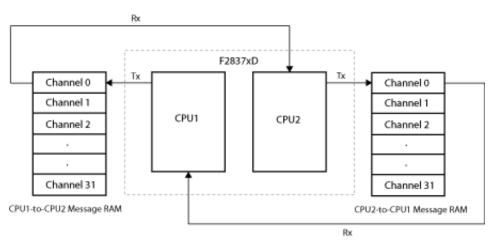

| Select CPU on page 1-38                                                                                                 | Select a CPU core to run the<br>generated code on a dual-<br>core processor, such as<br>F2837xD.              |                      |

| Boot From Flash (stand<br>alone execution) on page 1-<br>38                                                             | Specify if the application loads to the flash memory.                                                         | enabled              |

| Use custom linker command file on page 1-38                                                                             | Indicates that the custom<br>linker command file must be<br>used during the build action.                     | enabled              |

| Linker command file on page 1-38                                                                                        | The path to the memory<br>description file required<br>during linking.                                        |                      |

| CCS hardware configuration file on page 1-38                                                                            | The Code Composer<br>Studio <sup>™</sup> file required for<br>downloading the application<br>on the hardware. |                      |

| Enable DMA to access<br>ePWM Registers instead of<br>CLA on page 1-38                                                   | Select to access ePWM<br>Registers                                                                            |                      |

| Enable DMA to peripheral<br>frame 1 (ePWM, HRPWM,<br>eCAP, eQEP, DAC,CMPSS,<br>and SDFM) instead of CLA<br>on page 1-38 | Select to enable the DMA to<br>access peripheral frame 1                                                      |                      |

| Parameter                                                                                | Description                                                                                   | Default Value |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------|

| Enable DMA to peripheral<br>frame 2 (SPI and McBSP)<br>instead of CLA on page 1-<br>38   | Select to enable the DMA to access peripheral frame 2                                         |               |

| Enable FastRTS on page 1-<br>38                                                          | Enables use of optimized<br>floating point math<br>functions from C28x FPU<br>fastRTS library | enabled       |

| Remap ePWMs for DMA<br>access (Requires silicon<br>revision A and above) on<br>page 1-38 | Select to remap ePWMs<br>registers for DMA access                                             |               |

#### Clocking

| Parameter                                                     | Description                                                                                                                                                                                                                      | Default Value |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Desired CPU Clock in MHz<br>on page 1-42                      | Specify the desired CPU clock frequency (CLKIN).                                                                                                                                                                                 |               |

| Use internal oscillator on page 1-42                          | Use the internal zero pin oscillator on the CPU.                                                                                                                                                                                 | enabled       |

| Oscillator clock (OSCCLK)<br>frequency in MHz on page<br>1-42 | Oscillator frequency used in the processor.                                                                                                                                                                                      |               |

| Auto set PLL based on<br>OSCCLK and CPU clock on<br>page 1-42 | PLL values in PLLCR,<br>DIVSEL, and <b>Achievable</b><br><b>SYSCLKOUT in MHz</b> are<br>automatically calculated<br>based on the CPU clock<br>entered on the board.                                                              |               |

| PLL control register<br>(PLLCR) on page 1-42                  | If you select <b>Auto set PLL</b><br><b>based on OSCCLK and</b><br><b>CPU clock</b> , the auto-<br>calculated control register<br>value matches the specified<br>CPU clock value, based on<br>the oscillator clock<br>frequency. |               |

| PLL output divider (ODIV)<br>on page 1-42                     | Calculates SYSCLKOUT =<br>((OSCCLK×SYSPLLMULT)/<br>ODIV)/SYSDIVSEL.                                                                                                                                                              |               |

| Clock divider (DIVSEL) on<br>page 1-42                        | If you select <b>Auto set PLL</b><br><b>based on OSCCLK and</b><br><b>CPU clock</b> , the auto-<br>calculated control register<br>value matches the specified<br>CPU clock value, based on<br>the oscillator clock<br>frequency. |               |

| Parameter                                                                                                                   | Description                                                                                                                                                                                                             | Default Value |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Achievable SYSCLKOUT in<br>MHz = (OSCCLK×PLLCR)/<br>DIVSEL on page 1-42                                                     | The auto-calculated<br>feedback value that matches<br>the <b>Desired C28x CPU</b><br><b>clock in MHz</b> value, based<br>on the values of OSCCLK,<br>PLLCR, and DIVSEL.                                                 |               |

| Set the 'Achievable<br>SYSCLKOUT in MHz =<br>(OSCCLK*SYSPLLMULT)/<br>SYSDIVSEL' value<br>calculated in CPU1 on page<br>1-42 | Available only for CPU2 of<br>dual C28x core processors.<br>Value of this parameter<br>must be same as the value<br>of the parameter<br>Achievable SYSCLKOUT<br>in MHz =<br>(OSCCLK*PLLCR)/DIVSEL<br>(auto calculated). |               |

| Select the 'Low-Speed<br>Peripheral Clock Prescaler<br>(LSPCLK)' option used in<br>CPU1 on page 1-42                        | Available only for CPU2 of<br>dual C28x core processors.<br>Value of this parameter<br>must be same as the value<br>of the parameter Low-<br>Speed Peripheral Clock<br>Prescaler (LSPCLK)<br>specified in CPU1.         |               |

| Low-Speed Peripheral Clock<br>Prescaler (LSPCLK) on page<br>1-42                                                            | Prescaler value used to<br>calculate LSPCLK based on<br>SYSCLKOUT.                                                                                                                                                      |               |

| Low-Speed Peripheral Clock<br>(LSPCLK) in MHz on page 1-<br>42                                                              | The LSPCLK value<br>calculated using the<br>SYSCLKOUT and LSPCLK<br>Prescaler values.                                                                                                                                   |               |

| High-Speed Peripheral<br>Clock Prescaler (HSPCLK)<br>on page 1-42                                                           | Prescaler value used to<br>calculate HSPCLK based on<br>SYSCLKOUT.                                                                                                                                                      |               |

| Parameter                                                      | Description                                                                             | Default Value |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------|

| High-Speed Peripheral<br>Clock (HSPCLK) in MHz on<br>page 1-42 | The HSPCLK value<br>calculated using the<br>SYSCLKOUT and HSPCLK<br>Prescaler values.   |               |

| Analog Subsystem Clock<br>Prescaler (ASYSCLK) on<br>page 1-42  | Prescaler value used to<br>calculate ASYSCLK based<br>on SYSCLKOUT.                     |               |

| Analog Subsystem Clock<br>(ASYSCLK) in MHz on page<br>1-42     | The ASYSCLK value<br>calculated using the<br>SYSCLKOUT and ASYSCLK<br>Prescaler values. |               |

#### ADC\_x

| Parameter                                                                            | Description                                                                                                                                              | Default Value |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Select the CPU core which<br>controls ADC_x module on<br>page 1-46                   | The CPU core that controls the ADC module.                                                                                                               |               |

| ADC clock prescaler<br>(ADCCLK) on page 1-46                                         | The ADCCLK divider for the c2802x, c2803x, c2806x, F28M3x, F2807x, or F2837x processor.                                                                  |               |

| ADC clock frequency in<br>MHz on page 1-46                                           | The clock frequency for<br>ADC, which is auto<br>generated based on the<br>value you select in <b>ADC</b><br><b>clock prescaler</b><br><b>(ADCCLK)</b> . |               |

| ADC overlap of sample and<br>conversion<br>(ADC#NONOVERLAP) on<br>page 1-46          | Enable or disable overlap of sample and conversion.                                                                                                      |               |

| ADC clock prescaler<br>(ADCLKPS) on page 1-46                                        | The HSPCLK is divided by<br>ADCLKPS (a 4-bit value) as<br>the first step in deriving the<br>core clock speed of the ADC.                                 | 3             |

| ADC Core clock prescaler<br>(CPS) on page 1-46                                       | After dividing the HSPCLK<br>speed by the <b>ADC clock</b><br><b>prescaler (ADCLKPS)</b><br>value, divides the result by<br>2.                           | 1             |

| ADC Module clock (ADCCLK<br>= HSPCLK/ADCLKPS×2)/<br>(CPS+1)) in MHz on page 1-<br>46 | The ADC module clock,<br>which indicates the ADC<br>operating clock speed.                                                                               |               |

| Parameter                                                                                  | Description                                                                                                                                                                                       | Default Value |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Acquisition window<br>prescaler (ACQ_PS) on page<br>1-46                                   | Determine the width of the<br>sampling or acquisition<br>period. A higher value<br>indicates a wider sampling<br>period.                                                                          | 4             |

| Acquisition window size<br>((ACQ_PS+1)/ADCCLK) in<br>micro seconds/channel on<br>page 1-46 | Determine the duration for<br>which the sampling switch is<br>closed.                                                                                                                             |               |

| Offset on page 1-46                                                                        | Specify the offset value.                                                                                                                                                                         |               |

| Use external reference<br>2.048V on page 1-46                                              | Allows using a 2.048 V<br>external voltage reference.                                                                                                                                             |               |

| Use external reference on page 1-46                                                        | Allows using an external voltage reference.                                                                                                                                                       |               |

| Continuous mode on page 1-<br>46                                                           | When the ADC generates an<br>end of conversion (EOC)<br>signal, an ADCINT#<br>interrupt is generated. The<br>interrupt indicates whether<br>the previous interrupt flag<br>has been acknowledged. |               |

| ADC offset correction<br>(OFFSET_TRIM: -256 to<br>255) on page 1-46                        | The 280x ADC supports<br>offset correction using a 9-<br>bit value that it adds or<br>subtracts before the results<br>are available in the ADC<br>result registers.                               | Θ             |

| Parameter                           | Description                                                                                                                                                                                                                                                                                                                                                                                                      | Default Value              |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| VREFHI, VREFLO on page<br>1-46      | When you disable the <b>Use</b><br>external reference 2.048V<br>or External reference<br>option, the ADC logic uses a<br>fixed 0-3.3 V input range,<br>and VREFHI and VREFLO<br>are disabled. To interpret<br>the ADC input as a<br>ratiometric signal, select the<br>External reference option.<br>Then, set values for the<br>high-voltage reference<br>(VREFHI) and the low<br>voltage reference<br>(VREFLO). |                            |

| INT pulse control on page 1-<br>46  | Set the time when the ADC<br>sets ADCINTFLG ADCINTx<br>relative to the SOC and EOC<br>pulses.                                                                                                                                                                                                                                                                                                                    |                            |

| SOC high priority on page 1-46      | Enable SOC high priority mode.                                                                                                                                                                                                                                                                                                                                                                                   | All in round robin<br>mode |

| XINT2SOC external pin on page 1-46  | The pin to which the ADC sends the XINT2SOC pulse.                                                                                                                                                                                                                                                                                                                                                               |                            |

| ADCEXTSOC external pin on page 1-46 | The pin to which the ADC sends the ADCEXTSOC pulse.                                                                                                                                                                                                                                                                                                                                                              |                            |

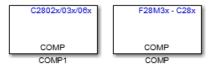

#### СОМР

| Parameter | Description                    | Default Value |

|-----------|--------------------------------|---------------|

|           | Assign COMP pin to a GPIO pin. |               |

#### DAC

| Parameter                                   | Description                                                                                                              | Default Value |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------|

| DACx reference voltage on page 1-50         | Select the reference voltage<br>for the DAC channel A, B, or<br>C.                                                       |               |

| DACx synchronization signal<br>on page 1-50 | Select the synchronization<br>signal to load the value from<br>the writable shadow register<br>into the active register. | SYSCLK        |

#### eCAN\_x

| Parameter                                                                                       | Description                                                                                                                                                           | Default Value |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| CAN module clock<br>frequency (= SYSCLKOUT)<br>in MHz on page 1-51                              | The clock for the enhanced CAN module.                                                                                                                                |               |

| CAN module clock<br>frequency (=SYSCLKOUT/2)<br>in MHz on page 1-51                             | The clock for the enhanced CAN module.                                                                                                                                |               |

| Baud rate prescaler (BRP: 2<br>to 256)/Baud rate prescaler<br>(BRP: 1 to 1024) on page 1-<br>51 | Scale the bit rate using this value.                                                                                                                                  |               |

| Time segment 1 (TSEG1) on<br>page 1-51                                                          | Set the value of time<br>segment 1. This value, with<br><b>TSEG2</b> and <b>Baud rate</b><br><b>prescaler</b> , determines the<br>length of a bit on the eCAN<br>bus. |               |

| Time segment 2 (TSEG2) on<br>page 1-51                                                          | Set the value of time<br>segment 2. This value, with<br><b>TSEG1</b> and <b>Baud rate</b><br><b>prescaler</b> , determines the<br>length of a bit on the eCAN<br>bus. |               |

| Baud rate (CAN Module<br>Clock/BRP/(TSEG1 + TSEG2<br>+1)) in bits/sec on page 1-<br>51          | CAN module communication<br>speed represented in bits/<br>second.                                                                                                     |               |

| SBG on page 1-51                                                                                | Set the message<br>resynchronization<br>triggering.                                                                                                                   |               |

| Parameter                           | Description                                                                                                                                            | Default Value |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| SJW on page 1-51                    | Set the synchronization<br>jump width, which<br>determines how many units<br>of TQ a bit can be shortened<br>or lengthened by when<br>resynchronizing. |               |

| SAM on page 1-51                    | Number of samples used by<br>the CAN module to<br>determine the CAN bus<br>level.                                                                      |               |

| Enhanced CAN Mode on<br>page 1-51   | Enable time stamping and<br>usage of Mailbox Numbers<br>16 through 31 in the C2000<br>eCAN blocks.                                                     |               |

| Self test mode on page 1-<br>51     | If you set this parameter to<br>True, the eCAN module<br>goes to loopback mode. The<br>loopback mode sends a<br>dummy acknowledge<br>message back.     | False         |

| Pin assignment (Tx) on page<br>1-51 | Assign the CAN transmit pin<br>to use with the eCAN_B<br>module.                                                                                       |               |

| Pin assignment (Rx) on page<br>1-51 | Assign the CAN receive pin<br>to use with the eCAN_B<br>module.                                                                                        |               |

#### eCAP

| Parameter                         | Description                    | Default Value |

|-----------------------------------|--------------------------------|---------------|

| ECAPx pin assignment on page 1-53 | Assign eCAP pin to a GPIO pin. |               |

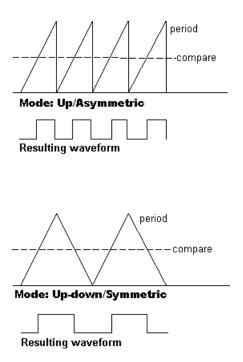

#### ePWM

| Parameter                                                                               | Description                                                                                                                                                                        | Default Value |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| EPWM clock divider<br>(EPWMCLKDIV) on page 1-<br>54                                     | Select the ePWM clock<br>divider.                                                                                                                                                  |               |

| Select the 'EPWM clock<br>divider (EPWMCLKDIV)'<br>option used for CPU1 on<br>page 1-54 | Available only for CPU2 of<br>dual C28x core processors.<br>Its value must be the same<br>as the value of the<br>parameter EPWM clock<br>divider (EPWMCLKDIV)<br>selected in CPU1. |               |

| TZx pin assignment on page 1-54                                                         | Assign the trip-zone input x<br>(TZx) to a GPIO pin.                                                                                                                               |               |

| SYNCI pin assignment on page 1-54                                                       | Assign the ePWM external<br>sync pulse input (SYNCI) to<br>a GPIO pin.                                                                                                             |               |

| SYNCO pin assignment on page 1-54                                                       | Assign the ePWM external<br>sync pulse output (SYNCO)<br>to a GPIO pin.                                                                                                            |               |

| PWM#x pin assignment on page 1-54                                                       | Assign the GPIO pin to the PWM#x module.                                                                                                                                           |               |

| GPTRIP#SEL pin<br>assignment(GPIO0~63) on<br>page 1-54                                  | Assign the ePWM trip-zone input to a GPIO pin.                                                                                                                                     |               |

| PWM1SYNCI/ GPTRIP6SEL<br>pin assignment on page 1-<br>54                                | Assign the ePWM sync pulse<br>input (SYNCI) to a GPIO pin.                                                                                                                         |               |

| DCxHTRIPSEL (Enter Hex<br>value between 0 and<br>0x6FFF) on page 1-54                   | Assign the <b>Digital</b><br><b>Compare A</b> high trip input<br>to a GPIO pin.                                                                                                    |               |

| DCxLTRIPSEL (Enter Hex<br>value between 0 and<br>0x6FFF) on page 1-54                   | Assign the <b>Digital</b><br><b>Compare A</b> low trip input<br>to a GPIO pin.                                                                                                     |               |

#### I2C

| Parameter                                                                                  | Description                                                                                                                  | Default Value |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------|

| Mode on page 1-57                                                                          | Configure the I2C module as Master or Slave.                                                                                 |               |

| Addressing format on page<br>1-57                                                          | In Slave mode, determines<br>the addressing format of the<br>I2C master and sets the I2C<br>module to the same mode.         |               |

| Own address register on<br>page 1-57                                                       | In Slave mode, enter the 7-<br>bit (0-127) or 10-bit (0-<br>1023) address that the I2C<br>module uses.                       |               |

| Bit count on page 1-57                                                                     | In Slave mode, sets the<br>number of bits in each data<br>byte the I2C module<br>transmits and receives.                     |               |

| Module clock prescaler<br>(IPSC: 0 to 255) on page 1-<br>57                                | In Master mode, enter a<br>value in the range 0-255,<br>inclusive, to configure the<br>model clock frequency.                |               |

| I2C Module clock frequency<br>(SYSCLKOUT / (IPSC+1)) in<br>Hz on page 1-57                 | Display the frequency the<br>I2C module uses internally.<br>To set this value, change the<br><b>Module clock prescaler</b> . |               |

| I2C Master clock frequency<br>(Module Clock Freq/(ICCL<br>+ICCH+10)) in Hz on page<br>1-57 | Display the master clock<br>frequency.                                                                                       |               |

| Master clock Low-time<br>divider (ICCL: 1 to 65535)<br>on page 1-57                        | In Master mode,<br>determines the duration of<br>the low state of the SCL on<br>the I2C bus.                                 |               |

| Parameter                                                            | Description                                                                                                                               | Default Value |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Master clock High-time<br>divider (ICCH: 1 to 65535)<br>on page 1-57 | In Master mode,<br>determines the duration of<br>the high state of the SCL on<br>the I2C bus.                                             |               |

| Enable loopback on page 1-<br>57                                     | In Master mode, enables or<br>disables digital loopback<br>mode.                                                                          |               |

| SDA pin assignment on page 1-57                                      | Select a GPIO pin as an I2C<br>data bidirectional port.                                                                                   |               |

| SCL pin assignment on page 1-57                                      | Select a GPIO pin as an I2C clock bidirectional port.                                                                                     |               |

| Enable Tx interrupt on page 1-57                                     | This parameter corresponds<br>to bit 5 (TXFFIENA) of the<br>I2C Transmit FIFO Register<br>(I2CFFTX).                                      |               |

| Tx FIFO interrupt level on<br>page 1-57                              | This parameter corresponds<br>to bits 4–0 (TXFFIL4-0) of<br>the I2C transmit FIFO<br>register (I2CFFTX).                                  |               |

| Enable Rx interrupt on page 1-57                                     | This parameter corresponds<br>to bit 5 (RXFFIENA) of the<br>I2C receive FIFO register<br>(I2CFFRX).                                       |               |

| Rx FIFO interrupt level on page 1-57                                 | This parameter corresponds<br>to bit 4-0 (RXFFIL4-0) of the<br>I2C receive FIFO register<br>(I2CFFRX).                                    |               |

| Enable system interrupt on page 1-57                                 | Select this parameter to<br>configure the five basic I2C<br>interrupt request<br>parameters in the interrupt<br>enable register (I2CIER). |               |

| Enable AAS interrupt on page 1-57                                    | Enable the addressed-as-<br>slave interrupt bit.                                                                                          |               |

| Parameter                          | Description                                         | Default Value |

|------------------------------------|-----------------------------------------------------|---------------|

| Enable SCD interrupt on page 1-57  | Enable the stop condition detected interrupt bit.   |               |

| Enable ARDY interrupt on page 1-57 | Enable the register-access-<br>ready interrupt bit. |               |

| Enable NACK interrupt on page 1-57 | Enable the no<br>acknowledgment interrupt<br>bit.   |               |

| Enable AL interrupt on page 1-57   | Enable the arbitration-lost interrupt bit.          |               |

#### SCI\_x

| Parameter                                                                      | Description                                                                                                         | Default Value |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------|

| Enable loopback on page 1-<br>63                                               | Enable the loopback<br>function for self-test and<br>diagnostics.                                                   |               |

| Suspension mode on page 1-<br>63                                               | The type of suspension to<br>use while debugging your<br>program with Code<br>Composer Studio.                      |               |

| Number of stop bits on page 1-63                                               | Specify the number of stop<br>bits transmitted.                                                                     |               |

| Parity mode on page 1-63                                                       | The type of parity to use.                                                                                          |               |

| Character length bits on page 1-63                                             | Length in bits of each<br>transmitted or received<br>character.                                                     | 8             |

| Desired baud rate in bits/sec<br>on page 1-63                                  | Specify the desired baud rate.                                                                                      |               |

| Baud rate prescaler (BRR =<br>(SCIHBAUD << 8)  <br>SCILBAUD)) on page 1-63     | Scale the SCI baud rate using this value.                                                                           |               |

| Closest achievable baud rate<br>(LSPCLK/(BRR+1)/8) in<br>bits/sec on page 1-63 | The closest achievable baud<br>rate, calculated based on<br>LSPCLK and BRR.                                         |               |

| Communication mode on page 1-63                                                | Select the mode for<br>transmitting and receiving<br>data.                                                          |               |

| Blocking mode on page 1-<br>63                                                 | If this option is enabled, the<br>system waits until data is<br>available to read (when data<br>length is reached). |               |

| Data byte order on page 1-<br>63                                               | Select an option to match<br>the endianness of the data<br>being moved.                                             |               |

| Parameter                        | Description                                                | Default Value |

|----------------------------------|------------------------------------------------------------|---------------|

| Pin assignment (Tx) on page 1-63 | Assign the SCI transmit pin<br>to use with the SCI module. |               |

| Pin assignment (Rx) on page 1-63 | Assign the SCI receive pin<br>to use with the SCI module.  |               |

#### SPI\_x

| Parameter                                                                       | Description                                                                                    | Default Value |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------|

| Mode on page 1-66                                                               | Set to Master or Slave.                                                                        |               |

| Desired baud rate in bits/sec<br>on page 1-66                                   | Specify the desired baud rate.                                                                 |               |

| Baud rate factor (SPIBRR:<br>between 3 and 127) on page<br>1-66                 | The value used to calculate the baud rate.                                                     |               |

| Closest achievable baud rate<br>(LSPCLK/(SPIBRR+1)) in<br>bits/sec on page 1-66 | The closest achievable baud<br>rate, calculated based on<br>LSPCLK and SPIBRR.                 |               |

| Suspension mode on page 1-<br>66                                                | The type of suspension to<br>use while debugging your<br>program with Code<br>Composer Studio. |               |

| Enable loopback on page 1-<br>66                                                | Enable the loopback<br>function for self-test and<br>diagnostics.                              |               |

| Enable 3-wire mode on page 1-66                                                 | Enables SPI communication<br>over three pins instead of<br>the normal four pins.               |               |

| Enable Tx interrupt on page 1-66                                                | Enable SPI transmit interrupt operation.                                                       |               |

| FIFO interrupt level (Tx) on page 1-66                                          | Set level for transmit FIFO interrupt.                                                         |               |

| Enable Rx interrupt on page 1-66                                                | Enable SPI receive interrupt operation.                                                        |               |

| FIFO interrupt level (Rx) on page 1-66                                          | Set level for receive FIFO interrupt.                                                          |               |

| FIFO transmit delay on page<br>1-66                                             | FIFO transmit delay (in<br>processor clock cycles) to<br>pause between data<br>transmissions.  |               |

| Parameter                        | Description                                   | Default Value |

|----------------------------------|-----------------------------------------------|---------------|

| SIMO pin assignment on page 1-66 | Assign the SPI (SIMO) to a<br>GPIO pin.       |               |

| SOMI pin assignment on page 1-66 | Assign the SPI value (SOMI)<br>to a GPIO pin. |               |

| CLK pin assignment on page 1-66  | Assign the CLK pin to a<br>GPIO pin.          |               |

| STE pin assignment on page 1-66  | Assign the SPI value (STE)<br>to a GPIO pin.  |               |

#### eQEP

| Parameter                          | Description                    | Default Value |

|------------------------------------|--------------------------------|---------------|

| EQEP#x pin assignment on page 1-68 | Assign eQEP pin to a GPIO pin. |               |

#### Watchdog

| Parameter                                                          | Description                                                                                                                                  | Default Value |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Enable watchdog on page 1-<br>69                                   | Enable the watchdog timer module.                                                                                                            |               |

| Counter clock on page 1-69                                         | Set the watchdog timer<br>period relative to OSCCLK/<br>512.                                                                                 |               |

| Timer period ((1/Counter<br>clock)×256) in seconds on<br>page 1-69 | Display the timer period in<br>seconds. This value<br>automatically updates when<br>you change the <b>Counter</b><br><b>clock</b> parameter. |               |

| Time out event on page 1-<br>69                                    | Configure the watchdog to<br>reset the processor or<br>generate an interrupt when<br>the software fails to reset<br>the watchdog counter.    |               |

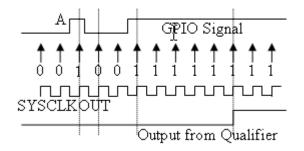

#### GPIO

| Parameter | Description                                                                                                    | Default Value |

|-----------|----------------------------------------------------------------------------------------------------------------|---------------|

|           | Use the GPIO pins for digital<br>input or output by<br>connecting to one of the<br>three peripheral I/O ports. |               |

| DMA | ch# |

|-----|-----|

|     |     |

| Parameter                         | Description                                                                                                                                             | Default Value |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Enable DMA channel on page 1-76   | Enable to edit the<br>configuration of a specific<br>DMA channel.                                                                                       |               |

| Data size on page 1-76            | Select the size of the data bit transfer.                                                                                                               |               |

| Interrupt source on page 1-<br>76 | Select the peripheral<br>interrupt that triggers a<br>DMA burst for the specified<br>channel.                                                           |               |

| SRC wrap on page 1-76             | Specify the number of<br>bursts before returning the<br>current source address<br>pointer to the <b>Source</b><br><b>Begin Address</b> value.           |               |

| DST wrap on page 1-76             | Specify the number of<br>bursts before returning the<br>current destination address<br>pointer to the <b>Destination</b><br><b>Begin Address</b> value. |               |

| SRC Begin address on page<br>1-76 | Set the starting address for<br>the current source address<br>pointer.                                                                                  |               |

| DST Begin address on page<br>1-76 | Set the starting address for<br>the current destination<br>address pointer.                                                                             |               |

| Burst on page 1-76                | Specify the number of 16-bit words in a burst, from 1 to 32.                                                                                            |               |

| Transfer on page 1-76             | Specify the number of<br>bursts in a transfer, from 1<br>to 65536.                                                                                      |               |

| Parameter                          | Description                                                                                                                                                                               | Default Value |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| SRC Burst step on page 1-<br>76    | Increment or decrement the<br>current address pointer by<br>this number of 16-bit words<br>before the next burst.                                                                         |               |

| DST Burst step on page 1-<br>76    | Increment or decrement the<br>current address pointer by<br>this number of 16-bit words<br>before the next burst.                                                                         |               |

| SRC Transfer step on page<br>1-76  | Increment or decrement the<br>current address pointer by<br>this number of 16-bit words<br>before the next transfer.                                                                      |               |

| DST Transfer step on page<br>1-76  | Increment or decrement the<br>current address pointer by<br>this number of 16-bit words<br>before the next transfer.                                                                      |               |

| SRC Wrap step on page 1-<br>76     | Increment or decrement the<br>SRC_BEG_ADDR address<br>pointer by this number of<br>16-bit words when a wrap<br>event occurs.                                                              |               |

| DST Wrap step on page 1-<br>76     | Increment or decrement the<br>DST_BEG_ADDR address<br>pointer by this number of<br>16-bit words when a wrap<br>event occurs.                                                              |               |

| Generate interrupt on page<br>1-76 | Enable this parameter to<br>have the DMA channel send<br>an interrupt to the CPU<br>through the Peripheral<br>Interrupt Expansion (PIE) at<br>the beginning or end of a<br>data transfer. |               |

| Parameter                                         | Description                                                                                                                                                                                             | Default Value |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Enable one shot mode on<br>page 1-76              | Enable this parameter to<br>have the DMA channel<br>complete an entire <i>transfer</i><br>in response to an interrupt<br>event trigger.                                                                 |               |

| Sync enable on page 1-76                          | Enable this parameter to<br>reset the DMA wrap counter<br>when the <b>Interrupt source</b><br>is set to SEQ1INT and sends<br>the ADCSYNC signal to the<br>DMA wrap counter.                             |               |

| Enable continuous mode on page 1-76               | Select this parameter to<br>leave the DMA channel<br>enabled upon completing a<br>transfer. The channel waits<br>for the next interrupt event<br>trigger.                                               |               |

| Enable DST sync mode on<br>page 1-76              | Enabling this parameter<br>resets the destination wrap<br>counter<br>(DST_WRAP_COUNT) when<br><b>Sync enable</b> is enabled and<br>the DMA module receives<br>the SEQ1INT interrupt/<br>ADCSYNC signal. |               |

| Set channel 1 to highest<br>priority on page 1-76 | Enable this option when<br>DMA channel 1 is<br>configured to handle high-<br>bandwidth data, such as<br>ADC data, and the other<br>DMA channels are<br>configured to handle lower-<br>priority data.    |               |

| Parameter                                 | Description                                                                                                                                                                                                                                         | Default Value |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Enable overflow interrupt<br>on page 1-76 | Enable this parameter to<br>have the DMA channel send<br>an interrupt to the CPU<br>through the PIE if the DMA<br>module receives a<br>peripheral interrupt while a<br>previous interrupt from the<br>same peripheral is waiting<br>to be serviced. |               |

#### EMIF#

| Parameter                                                              | Description                                                                                                                                       | Default Value |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| EMIF clock divider<br>(EMIF1CLKDIV) on page 1-<br>84                   | Clock divider for clock<br>frequency generation.                                                                                                  | SYSCLKOUT/2   |

| Enable CS0 for Synchronous<br>memory on page 1-84                      | Chip select (CS0) to interface with the SDRAM.                                                                                                    | off           |

| Enable CS# for<br>Asynchronous memory on<br>page 1-84                  | Chip select (CS2/CS3/CS4)<br>to interface with the<br>asynchronous RAM.                                                                           | off           |

| SDRAM Column address<br>bits on page 1-84                              | Value of the column address<br>bits or the required page<br>size of the connected<br>SDRAM.                                                       | 8             |

| Number of internal SDRAM<br>banks on page 1-84                         | Number of memory banks<br>inside the connected<br>SDRAM.                                                                                          | 3             |

| SDRAM data bus width in<br>bits on page 1-84                           | Data bus width of the connected SDRAM.                                                                                                            | 16            |

| Refresh to active command<br>delay cycles (T_RFC) on<br>page 1-84      | Minimum number of<br>EM#CLK cycles from the<br>refresh or load mode<br>command to the refresh or<br>activate command in the<br>connected SDRAM.   | 3             |

| Row precharge to Active<br>command delay cycles<br>(T_RP) on page 1-84 | Minimum number of<br>EM#CLK cycles required<br>from the row precharge<br>command to the activate or<br>refresh command in the<br>connected SDRAM. | 1             |

| Parameter                                                                                 | Description                                                                                                                                              | Default Value |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Active to read or write<br>command delay cycles<br>(T_RCD) on page 1-84                   | Minimum number of<br>EM#CLK cycles from the<br>activate command to the<br>read or write command in<br>the connected SDRAM.                               | 2             |

| Last write to row precharge<br>command delay cycles<br>(T_WR) on page 1-84                | Minimum number of<br>EM#CLK cycles from the<br>last write transfer or last<br>data in command to the row<br>precharge command in the<br>connected SDRAM. | 1             |

| Active to precharge<br>command delay cycles<br>(T_RAS) on page 1-84                       | Minimum number of<br>EM#CLK cycles from the<br>activate command to the<br>row precharge command in<br>the connected SDRAM.                               | 4             |

| Active to active command<br>delay cycles (T_RC) on page<br>1-84                           | Minimum number of<br>EM#CLK cycles from an<br>activate command to the<br>next activate command in<br>the same bank in the<br>connected SDRAM.            | 6             |

| Active one bank to active<br>another bank command<br>delay cycles (T_RRD) on<br>page 1-84 | Minimum number of<br>EM#CLK cycles from an<br>activate command in one<br>bank to an activate<br>command in a different bank<br>in the connected SDRAM.   | 1             |

| Self-refresh exit to other<br>command delay cycles<br>(T_XSR) on page 1-84                | Minimum number of<br>EM#CLK cycles from the<br>self refresh exit command to<br>any other command in the<br>connected SDRAM.                              | 7             |

| SDRAM refresh period<br>(tRefreshPeriod) in ms on<br>page 1-84                            | Defines the rate at which<br>the connected SDRAM<br>refreshes.                                                                                           | 64            |

| Parameter                                               | Description                                                                                                                                      | Default Value |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| SDRAM CAS Latency on page 1-84                          | CAS latency required to<br>access the connected<br>SDRAM.                                                                                        | 3             |

| Asynchronous mode on page<br>1-84                       | Asynchronous mode for the connected asynchronous memory.                                                                                         | Normal        |

| Asynchronous data bus<br>width in bits on page 1-84     | Data bus width of the connected asynchronous memory.                                                                                             | 16            |

| Read strobe setup cycles<br>(R_SETUP) on page 1-84      | Number of EM#CLK cycles<br>from the EMIF chip select to<br>the pin enable for<br>asynchronous memory<br>assert.                                  | 15            |

| Read strobe duration cycles<br>(R_STROBE) on page 1-84  | Number of EM#CLK cycles<br>during which the pin enable<br>for the asynchronous<br>memory is held active.                                         | 64            |

| Read strobe hold cycles<br>(R_HOLD) on page 1-84        | Number of EM#CLK cycles<br>during which the EMIF chip<br>select is held active after pin<br>enable for the asynchronous<br>memory is deasserted. | 7             |

| Write strobe setup cycles<br>(W_SETUP) on page 1-84     | Number of EM#CLK cycles<br>from the EMIF chip select to<br>the write enable for the<br>asynchronous memory<br>assert.                            | 15            |

| Write strobe duration cycles<br>(W_STROBE) on page 1-84 | Number of EM#CLK cycles<br>during which the write<br>enable for the asynchronous<br>memory is held active.                                       | 63            |

| Parameter                                                                                         | Description                                                                                                                                                                                                 | Default Value |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Write strobe hold cycles<br>(W_HOLD) on page 1-84                                                 | Number of EM#CLK cycles<br>during which the EMIF chip<br>select is held active after<br>write enable for the<br>asynchronous memory is<br>deasserted.                                                       | 7             |

| Turn around cycles (TA) on<br>page 1-84                                                           | Number of EM#CLK cycles<br>between the end of one<br>asynchronous memory<br>access and the start of<br>another asynchronous<br>memory access.                                                               | 3             |

| Enable extended wait mode<br>on page 1-84                                                         | Enable the extended wait<br>option for the asynchronous<br>memory.                                                                                                                                          | off           |

| Maximum extended wait<br>cycles for Asynchronous<br>memory (MAX_EXT_WAIT)<br>[0-255] on page 1-84 | EMIF waits for<br>(MAX_EXT_WAIT+1) * 16<br>clock cycles before the<br>asynchronous cycle is<br>terminated.                                                                                                  | 128           |

| Pin polarity of extended wait<br>on page 1-84                                                     | Make EMIF wait if the pin is low or high.                                                                                                                                                                   | High          |

| Enable wait rise interrupt<br>on page 1-84                                                        | Get an interrupt based on<br>the detection of a rising<br>edge on the EM#WAIT pin.                                                                                                                          | off           |

| Enable timeout interrupt on<br>page 1-84                                                          | Get an interrupt when the<br>EM#WAIT pin does not<br>become inactive within the<br>number of cycles defined in<br>Maximum extended wait<br>cycles for Asynchronous<br>memory<br>(MAX_EXT_WAIT) [0-<br>255]. | off           |

| Parameter | Description                                                                               | Default Value |

|-----------|-------------------------------------------------------------------------------------------|---------------|

| 1 0       | Get an interrupt when there<br>is an invalid cache line size<br>or illegal memory access. | off           |

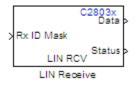

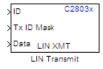

#### LIN

| Parameter                                                                   | Description                                                                                                               | Default Value                              |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| LIN Module clock frequency<br>(LM_CLK = SYSCLKOUT/2)<br>in MHz on page 1-91 | Display the frequency of the<br>LIN module clock in MHz.                                                                  |                                            |

| Enable loopback on page 1-<br>91                                            | Enable LIN loopback<br>testing.                                                                                           |                                            |

| Suspension mode on page 1-<br>91                                            | Use this option to configure<br>how the LIN state machine<br>behaves while you debug<br>the program using an<br>emulator. | Free_run                                   |

| Parity mode on page 1-91                                                    | Use this option to configure parity checking.                                                                             | None                                       |

| Frame length bytes on page<br>1-91                                          | Set the number of data<br>bytes in the response field,<br>from 1-8 bytes.                                                 | 8                                          |

| Baud rate prescaler (P:<br>0-16777215) on page 1-91                         | To set the LIN baud<br>manually, enter a prescaler<br>value from 0-16777215.                                              | 15                                         |

| Baud rate fractional divider<br>(M: 0-15) on page 1-91                      | To set the LIN baud<br>manually, enter a fractional<br>divider value from 0–15.                                           | 4                                          |

| Baud rate (FLINCLK =<br>LM_CLK/(16×(P+1+M/16))<br>in bits/sec on page 1-91  | Display the baud rate.                                                                                                    |                                            |

| Communication mode on<br>page 1-91                                          | Enable or disable the LIN<br>module from using the ID-<br>field bits ID4 and ID5 for<br>length control.                   | ID4 and ID5 not used<br>for length control |

| Data byte order on page 1-<br>91                                            | Set the endianness of the<br>LIN message data bytes.                                                                      | Little_Endian                              |

| Data swap width on page 1-<br>91                                            | Set the width for data swap.                                                                                              |                                            |

| Parameter                                                    | Description                                                                                                                             | Default Value      |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Pin assignment (Tx) on page 1-91                             | Map the LINTX output to a specific GPIO pin.                                                                                            | GPI09              |

| Pin assignment (Rx) on page 1-91                             | Map the LINRX input to a specific GPIO pin.                                                                                             | GPI011             |

| LIN mode on page 1-91                                        | Set the LIN module as a master or a slave.                                                                                              | Slave              |

| ID filtering on page 1-91                                    | Select the type of mask<br>filtering comparison the LIN<br>module performs.                                                             | ID slave task byte |

| ID byte on page 1-91                                         | If you set <b>ID filtering</b> as <b>ID</b><br>byte, use this option to set<br>the ID BYTE, also known as<br>the "LIN mode message ID". | 0x3A               |

| ID slave task byte on page<br>1-91                           | If you set <b>ID filtering</b> to <b>ID</b><br>slave task byte, use this<br>option to set the ID-<br>SlaveTask BYTE.                    | 0x30               |

| Checksum type on page 1-<br>91                               | Select the checksum type.                                                                                                               | Classic            |

| Enable multibuffer mode on page 1-91                         | When you select this check<br>box, the LIN node uses<br>transmit and receive buffers<br>instead of just one register.                   | Selected           |

| Enable baud rate adapt<br>mode on page 1-91                  | This option is displayed<br>when you set <b>LIN mode</b> to<br>Slave.                                                                   | Not selected       |

| Inconsistent synch field<br>error interrupt on page 1-<br>91 | If you enable this option, the<br>slave node generates<br>interrupts when it detects<br>irregularities in the synch<br>field.           | Disabled           |

| Parameter                                                    | Description                                                                                                                                                              | Default Value |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| No response error interrupt<br>on page 1-91                  | If you enable this option, the<br>LIN module generates an<br>interrupt if it does not<br>receive a complete response<br>from the master node within<br>a timeout period. | Disabled      |

| Timeout after 3 wakeup<br>signals interrupt on page 1-<br>91 | When enabled, the slave<br>node generates an interrupt<br>when it sends three wakeup<br>signals to the master node<br>and does not receive a<br>header in response.      | Disabled      |

| Timeout after wakeup signal<br>interrupt on page 1-91        | When enabled, the slave<br>node generates an interrupt<br>when it sends a wakeup<br>signal to the master node<br>and does not receive a<br>header in response.           | Disabled      |

| Timeout interrupt on page<br>1-91                            | When enabled, the slave<br>node generates an interrupt<br>after 4 seconds of inactivity<br>on the LIN bus.                                                               | Disabled      |

| Wakeup interrupt on page 1-<br>91                            | The LIN slave mode<br>generates a wakeup<br>interrupt based on a request<br>or condition.                                                                                | Disabled      |

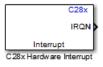

### **External Interrupt**

| Parameter                       | Description                                 | Default Value |

|---------------------------------|---------------------------------------------|---------------|

| XINT# GPIO on page 1-97         | Set the GPIO pin for<br>external interrupt. |               |

| XINT# Polarity on page 1-<br>97 | Set the polarity for external interrupt.    |               |

#### External Mode

| Parameter                            | Description                                                                                                                           | Default Value |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Communication interface on page 1-98 | Use the serial option to<br>run your model in external<br>mode with serial<br>communication.                                          |               |

| Serial port on page 1-98             | Enter the COM port used by the target hardware.                                                                                       |               |

| Verbose on page 1-98                 | Select to view the external<br>mode execution progress<br>and updates in the<br>Diagnostic Viewer or in the<br>MATLAB command window. |               |

#### **Execution Profiling**

| Parameter                   | Description                   | Default Value |

|-----------------------------|-------------------------------|---------------|

| Number of profiling samples |                               |               |

| to collect on page 1-99     | profiling samples to collect. |               |

#### SD Card Logging

| Parameter                                        | Description                                                                                | Default Value                                              |

|--------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Enable MAT-file logging on SD card on page 1-100 | Enables the MAT-file logging for SD card.                                                  | off                                                        |

| SPI module on page 1-100                         | Select the desired interface<br>on which the SD card is<br>connected to hardware<br>board. |                                                            |