### Applied Classical and Modern Control System Design

Richard Tymerski Frank Rytkonen Andrew Chuinard Portland State University Department of Electrical and Computer Engineering Portland, Oregon, USA ii

## Preface

This is the preface.

iv

# Contents

| Ι | Cla               | assical Control                                                            | 1         |

|---|-------------------|----------------------------------------------------------------------------|-----------|

| 1 | Intr              | oduction                                                                   | 3         |

|   | 1.1               | Introduction(ADD CONTENT)                                                  | 3         |

| 2 | The               | System                                                                     | 5         |

| 4 | 2.1               | Introduction                                                               | 5         |

|   | $\frac{2.1}{2.2}$ | The Plant: Buck Converter                                                  | 6         |

|   | 2.2               | 2.2.1 Introduction                                                         | 6         |

|   |                   | 2.2.1       Introduction         2.2.2       Transfer Function Derivations | 6         |

|   | 2.3               | Pulse-width Modulator                                                      | 14        |

|   | 2.0<br>2.4        | Summary                                                                    | 15        |

|   | 2.4               |                                                                            | 10        |

| 3 | Bod               | le Plots                                                                   | 19        |

|   |                   | 3.0.1 Bode Plots                                                           | 20        |

| 4 | Sing              | gle Loop Voltage Mode Control                                              | <b>27</b> |

|   | 4.1               | Introduction                                                               | 27        |

|   | 4.2               | Buck Converter System Models                                               | 28        |

|   |                   | 4.2.1 General Model                                                        | 28        |

|   |                   | 4.2.2 Simplified System Model                                              | 28        |

|   |                   | 4.2.3 Design Targets                                                       | 29        |

|   |                   | 4.2.4 Buck Converter Model Analysis                                        | 29        |

|   | 4.3               | Uncompensated System                                                       | 30        |

|   | 4.4               | Dominant Pole Compensation                                                 | 34        |

|   | 4.5               | Dominant Pole Compensation with Zero                                       | 42        |

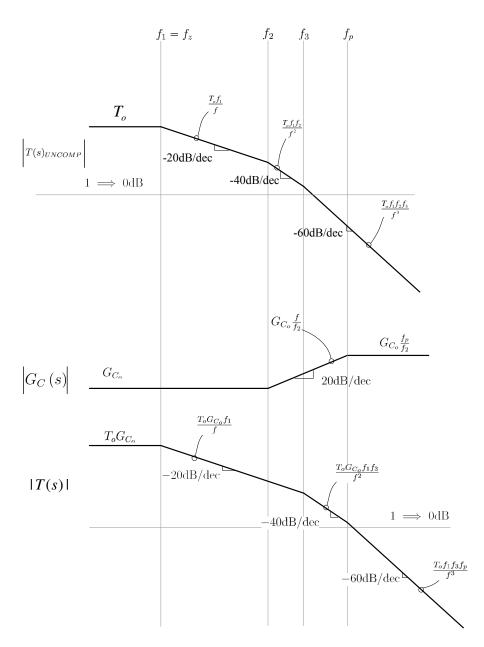

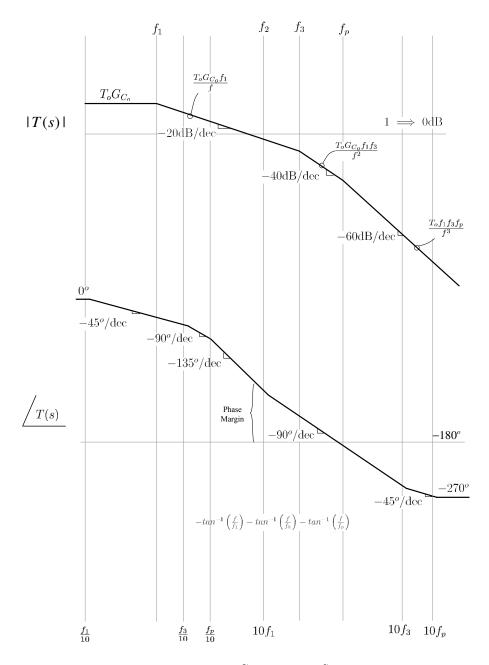

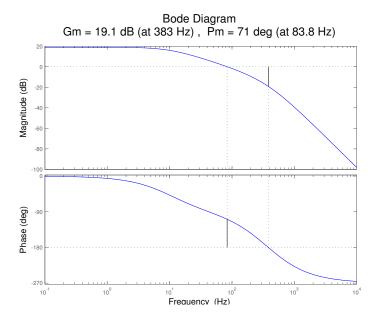

|   | 4.6               | Lead Compensation                                                          | 46        |

|   | 4.7               | Dominant Pole with Lead Compensation                                       | 51        |

|   |                   | 4.7.1 Design 1: Zero $f_1 = 500$ Hz                                        | 53        |

|   |                   | 4.7.2 Design 2: Zero $f_1 = 150$ Hz                                        | 56        |

|   | 4.8               | Extended Bandwidth Design                                                  | 59        |

|   | 4.9               | Conclusion                                                                 | 65        |

|   |                   | 4.9.1 Compensator Circuits                                                 | 68        |

|   | 4.10              | MATLAB Code                                                                | 69        |

#### CONTENTS

| <b>5</b>    | Worked Examples 7                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                     |

|-------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 5.1                                                                                      | Stability Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73                                                                                                                                                                                  |

|             |                                                                                          | 5.1.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73                                                                                                                                                                                  |

|             |                                                                                          | 5.1.2 Stability Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73                                                                                                                                                                                  |

|             |                                                                                          | 5.1.3 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 77                                                                                                                                                                                  |

|             |                                                                                          | 5.1.4 MATLAB Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 77                                                                                                                                                                                  |

|             | 5.2                                                                                      | Design Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80                                                                                                                                                                                  |

|             |                                                                                          | 5.2.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80                                                                                                                                                                                  |

|             |                                                                                          | 5.2.2 Uncompensated System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80                                                                                                                                                                                  |

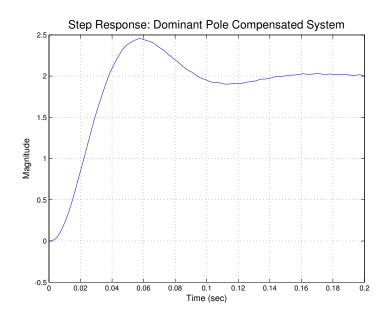

|             |                                                                                          | 5.2.3 Dominant Pole Compensated System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 82                                                                                                                                                                                  |

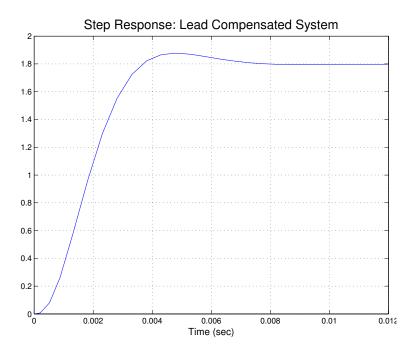

|             |                                                                                          | 5.2.4 Lead Compensated System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 94                                                                                                                                                                                  |

|             |                                                                                          | 5.2.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100                                                                                                                                                                                 |

|             |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100                                                                                                                                                                                 |

|             |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                     |

| 6           | Dro                                                                                      | op and Multi-Loop Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107                                                                                                                                                                                 |

|             | 6.1                                                                                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 108                                                                                                                                                                                 |

|             | 6.2                                                                                      | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 108                                                                                                                                                                                 |

|             |                                                                                          | 6.2.1 Passive Droop Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 108                                                                                                                                                                                 |

|             |                                                                                          | 6.2.2 Active Droop Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 115                                                                                                                                                                                 |

|             |                                                                                          | 6.2.3 Voltage Mode Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 120                                                                                                                                                                                 |

|             | 6.3                                                                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 132                                                                                                                                                                                 |

|             | 6.4                                                                                      | MATLAB Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 132                                                                                                                                                                                 |

|             |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                     |

|             |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                     |

| тт          | •                                                                                        | Is down Constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 4 9                                                                                                                                                                               |

| II          | $\mathbf{N}$                                                                             | Iodern Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 143                                                                                                                                                                                 |

|             |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                     |

| II<br>7     |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 143 $145$                                                                                                                                                                           |

|             | Inti                                                                                     | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                     |

| 7           | Inti                                                                                     | oduction<br>tem Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $145\\147$                                                                                                                                                                          |

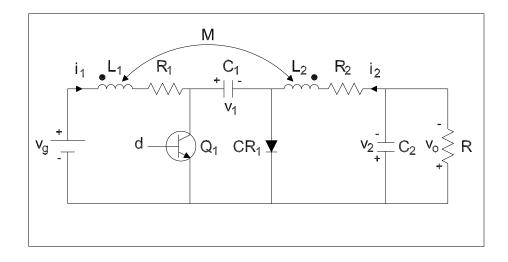

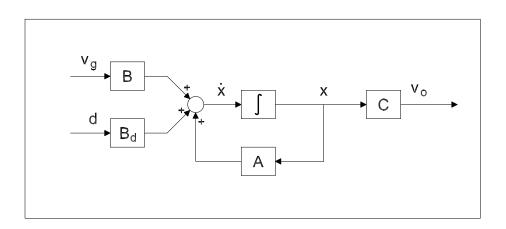

| 7           | Intr<br>Sys<br>8.1                                                                       | oduction<br>tem Analysis<br>The Ćuk Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 145<br>147<br>147                                                                                                                                                                   |

| 7           | Intı<br>Sys                                                                              | roduction<br>tem Analysis<br>The Ćuk Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>145</b><br><b>147</b><br>147<br>149                                                                                                                                              |

| 7           | Intr<br>Sys<br>8.1<br>8.2                                                                | roduction<br>tem Analysis<br>The Ćuk Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ol> <li>145</li> <li>147</li> <li>147</li> <li>149</li> <li>150</li> </ol>                                                                                                         |

| 7           | <b>Intr</b><br><b>Sys</b><br>8.1<br>8.2<br>8.3<br>8.4                                    | roduction         tem Analysis         The Ćuk Converter         Open Loop Performance of the Ćuk Converter         Controllability and Stabilizability         Observability and Detectability                                                                                                                                                                                                                                                                                                                                              | <b>145</b><br><b>147</b><br>147<br>149<br>150<br>151                                                                                                                                |

| 7           | Intr<br>Sys<br>8.1<br>8.2<br>8.3                                                         | coduction         tem Analysis         The Ćuk Converter         Open Loop Performance of the Ćuk Converter         Controllability and Stabilizability         Observability and Detectability         Controlling the Ćuk Converter                                                                                                                                                                                                                                                                                                        | <ol> <li>145</li> <li>147</li> <li>147</li> <li>149</li> <li>150</li> <li>151</li> <li>151</li> </ol>                                                                               |

| 7           | <b>Intr</b><br><b>Sys</b><br>8.1<br>8.2<br>8.3<br>8.4                                    | coduction         tem Analysis         The Ćuk Converter         Open Loop Performance of the Ćuk Converter         Controllability and Stabilizability         Observability and Detectability         Controlling the Ćuk Converter         8.5.1                                                                                                                                                                                                                                                                                          | <ol> <li>145</li> <li>147</li> <li>149</li> <li>150</li> <li>151</li> <li>151</li> <li>152</li> </ol>                                                                               |

| 7           | <b>Intr</b><br><b>Sys</b><br>8.1<br>8.2<br>8.3<br>8.4                                    | roduction         tem Analysis         The Ćuk Converter         Open Loop Performance of the Ćuk Converter         Controllability and Stabilizability         Observability and Detectability         Controlling the Ćuk Converter         8.5.1         Time Domain Specifications         8.5.2                                                                                                                                                                                                                                         | <ol> <li>145</li> <li>147</li> <li>149</li> <li>150</li> <li>151</li> <li>151</li> <li>152</li> <li>152</li> </ol>                                                                  |

| 7           | <b>Intr</b><br><b>Sys</b><br>8.1<br>8.2<br>8.3<br>8.4                                    | coduction         tem Analysis         The Ćuk Converter         Open Loop Performance of the Ćuk Converter         Controllability and Stabilizability         Observability and Detectability         Controlling the Ćuk Converter         8.5.1                                                                                                                                                                                                                                                                                          | <ol> <li>145</li> <li>147</li> <li>149</li> <li>150</li> <li>151</li> <li>151</li> <li>152</li> <li>152</li> </ol>                                                                  |

| 7           | <b>Int</b><br><b>Sys</b><br>8.1<br>8.2<br>8.3<br>8.4<br>8.5                              | roduction         tem Analysis         The Ćuk Converter         Open Loop Performance of the Ćuk Converter         Controllability and Stabilizability         Observability and Detectability         Controlling the Ćuk Converter         8.5.1         Time Domain Specifications         8.5.2         Frequency Domain Specifications         8.5.3         Control Effort Constraints                                                                                                                                                | <ol> <li>145</li> <li>147</li> <li>149</li> <li>150</li> <li>151</li> <li>151</li> <li>152</li> <li>152</li> </ol>                                                                  |

| 7           | <b>Int</b><br><b>Sys</b><br>8.1<br>8.2<br>8.3<br>8.4<br>8.5                              | roduction         tem Analysis         The Ćuk Converter         Open Loop Performance of the Ćuk Converter         Controllability and Stabilizability         Observability and Detectability         Controlling the Ćuk Converter         8.5.1         Time Domain Specifications         8.5.2         Frequency Domain Specifications         8.5.3         Control Effort Constraints                                                                                                                                                | <ol> <li>145</li> <li>147</li> <li>147</li> <li>150</li> <li>151</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> </ol>                           |

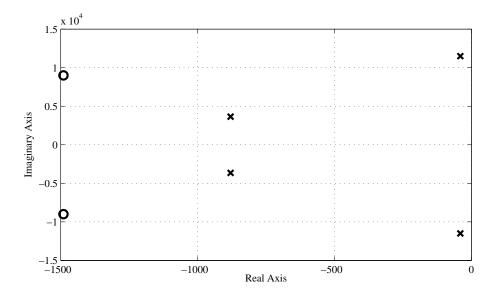

| 7           | Intr<br>Sys<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5                                           | coduction         tem Analysis         The Ćuk Converter         Open Loop Performance of the Ćuk Converter         Controllability and Stabilizability         Observability and Detectability         Controlling the Ćuk Converter         8.5.1         Time Domain Specifications         8.5.2         Frequency Domain Specifications         8.5.3         Control Effort Constraints         e Placement         Pole Placement via Ackermann's Formula                                                                             | <ol> <li>145</li> <li>147</li> <li>149</li> <li>150</li> <li>151</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> </ol> |

| 7           | <b>Intr</b><br><b>Sys</b><br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br><b>Pol</b><br>9.1        | roduction         tem Analysis         The Ćuk Converter         Open Loop Performance of the Ćuk Converter         Controllability and Stabilizability         Observability and Detectability         Observability and Detectability         Controlling the Ćuk Converter         8.5.1         Time Domain Specifications         8.5.2         Frequency Domain Specifications         8.5.3         Control Effort Constraints                                                                                                        | <ol> <li>145</li> <li>147</li> <li>149</li> <li>150</li> <li>151</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> </ol> |

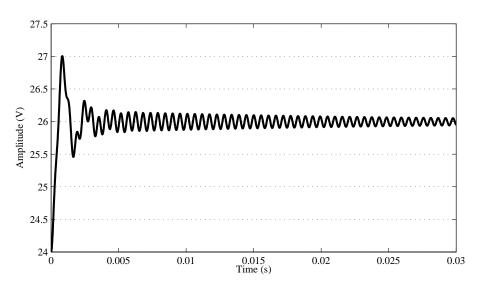

| 7<br>8<br>9 | <b>Intr</b><br><b>Sys</b><br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br><b>Pol</b><br>9.1<br>9.2 | <b>boduction tem Analysis</b> The Ćuk Converter         Open Loop Performance of the Ćuk Converter         Controllability and Stabilizability         Observability and Detectability         Controlling the Ćuk Converter         S.5.1         Time Domain Specifications         8.5.2         Frequency Domain Specifications         8.5.3         Control Effort Constraints         Placement         Pole Placement via Ackermann's Formula         Ćuk Converter with State Feedback Compensator                                  | <ol> <li>145</li> <li>147</li> <li>149</li> <li>150</li> <li>151</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> </ol> |

| 7<br>8<br>9 | Intr<br>Sys<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>Pol<br>9.1<br>9.2<br>Inte              | tem Analysis         The Ćuk Converter         Open Loop Performance of the Ćuk Converter         Controllability and Stabilizability         Observability and Detectability         Observability and Detectability         Controlling the Ćuk Converter         S.5.1         Time Domain Specifications         8.5.2         Frequency Domain Specifications         8.5.3         Control Effort Constraints         e Placement         Pole Placement via Ackermann's Formula         Čuk Converter with State Feedback Compensator | <ol> <li>145</li> <li>147</li> <li>149</li> <li>150</li> <li>151</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>152</li> <li>158</li> <li>158</li> </ol>              |

vi

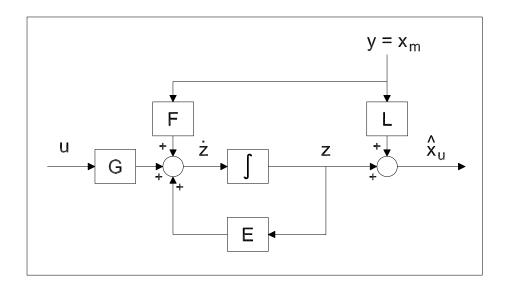

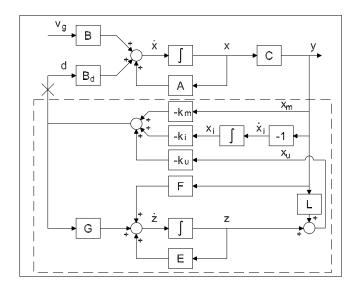

| 11 State Estimation                                  | 169        |  |

|------------------------------------------------------|------------|--|

| 11.1 Full-Order State Estimators                     | 169        |  |

| 11.2 Full-Order Estimator-Based Compensator          | 170        |  |

| 11.3 Reduced-Order State Estimators                  |            |  |

| 11.4 Reduced-Order Estimator-Based Compensator       |            |  |

| r                                                    |            |  |

| 12 Linear Quadratic Optimal Control                  | 179        |  |

| 12.1 Linear Quadratic Regulators                     | 179        |  |

| 12.2 Ćuk Converter with LQR Compensator              |            |  |

| 12.3 Linear Quadratic Gaussian Regulators            |            |  |

| 12.4 Ćuk Converter with LQG Compensator              |            |  |

| 12.5 Control with LQG/LTR Compensators               |            |  |

|                                                      | 101        |  |

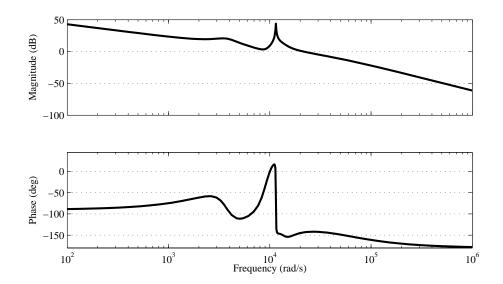

| 13 Compensator Order Reduction                       | 189        |  |

| 13.1 Model Reduction of the LQGI/LTR Compensator     | 189        |  |

| 13.2 A Reduced-Order LQGI/LTR Compensator            |            |  |

| • , •                                                |            |  |

| 14 Compensator Implementation                        | 199        |  |

| 14.1 MRLQGI/LTR Compensator Construction             | 199        |  |

| 14.2 MRROLQGI/LTR Compensator Construction           |            |  |

|                                                      |            |  |

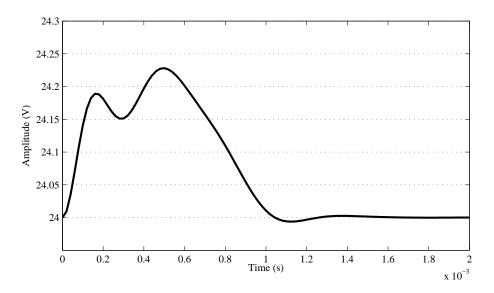

| 15 Power Electronic Circuit Simulation               | <b>203</b> |  |

| 15.1 Simulating the Controlled Ćuk Converter in PECS | 203        |  |

|                                                      |            |  |

| 16 Conclusion                                        | 207        |  |

|                                                      |            |  |

| Appendices                                           | 209        |  |

| Routh-Hurwitz Stability Analysis 211                 |            |  |

| Routh-Hurwitz Stability Analysis 21                  |            |  |

CONTENTS

viii

# Part I Classical Control

### Chapter 1

# Introduction

1.1 Introduction(ADD CONTENT)

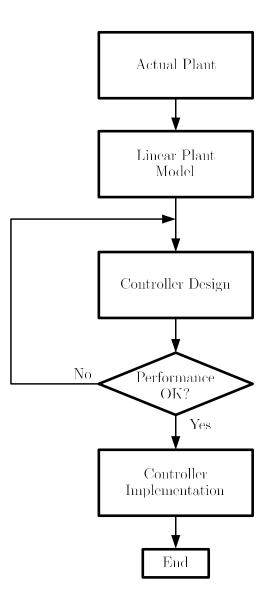

Figure 1.1: Design Flow Diagram

### Chapter 2

### The System

#### 2.1 Introduction

In this chapter, the parameters for an example control system will be defined and derived. From the parameters of this example system, subsequent chapters will be devoted to applying control design techniques to optimize system performance parameters.

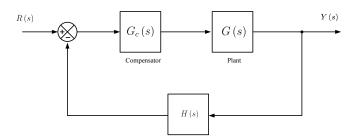

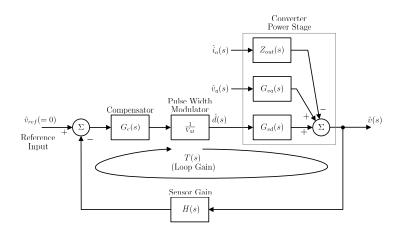

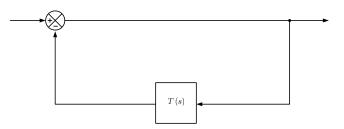

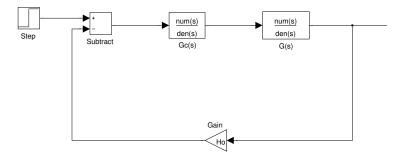

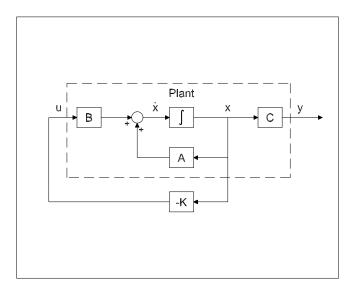

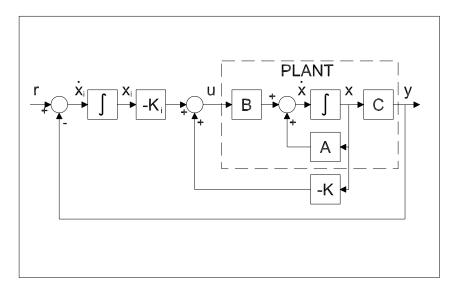

A control system begins with a model for plant, that has at least one particular parameter to be controlled. To control the plant, the parameter to be controlled is compared to a stable reference value and the difference is input to an error amplifier. The error amplifier then commands the plant, controlling the desired plant parameter. A basic diagram illustrating this architecture is shown in Figure 5.8.

Figure 2.1: Feedback System Block Diagram

#### 2.2 The Plant: Buck Converter

#### 2.2.1 Introduction

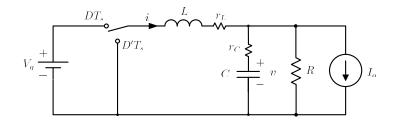

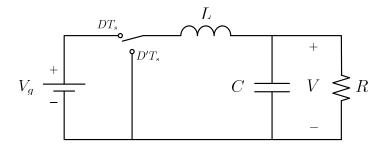

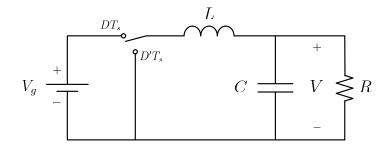

The fundamental item in every control system is the plant, the item that is to be controlled. In this section, the plant will be defined as a buck converter, a switched mode DC power supply.

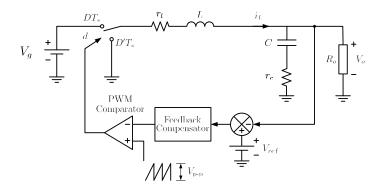

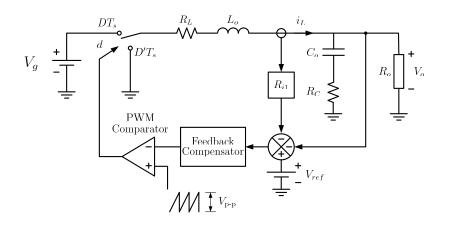

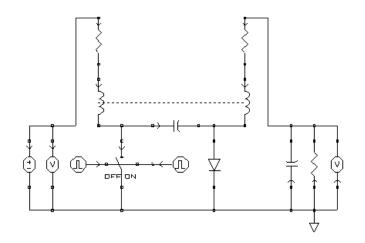

Figure 2.2: Buck Converter Circuit System Diagram

The buck regulator, which is shown complete in Figure 2.2 including circuit losses and feedback compensation, is a basic switched mode power supply. The buck regulator acts to reduce the steady state output voltage based on an applied duty cycle of applied input voltage. The duty cycle is switched at a frequency higher than the resonant frequency LC tank on the output. The output filter allows the circuit to convert the input voltage to a lower output voltage with minimal circuit losses.

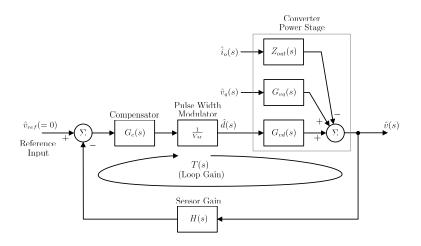

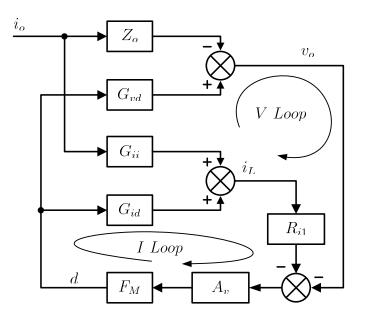

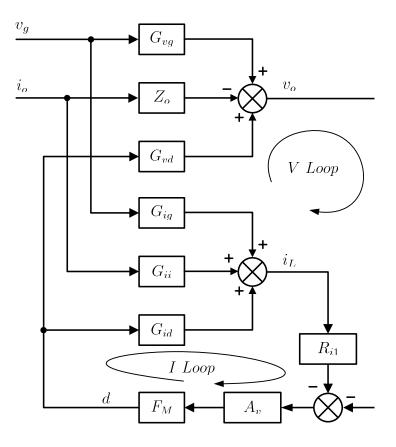

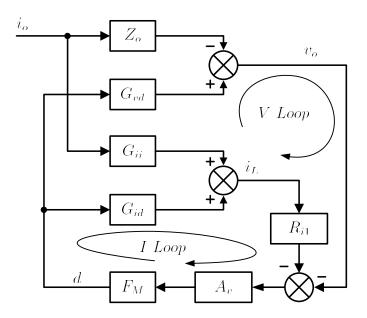

The complete system block diagram for the buck regulator is shown in Figure 4.1. The output voltage of the system is fed back to a reference (reduced by H(s)), and the difference (error signal) is fed to a compensator which drives a pulse-width modulator to control the output voltage. Additionally, this model includes disturbance inputs in terms of step loading and input voltage variation for design characterization.

#### 2.2.2 Transfer Function Derivations

To model the plant based on the diagram of Figure 4.1, three transfer functions are required to be derived. The transfer function are the control to output  $G_{vd}(s)$ , input voltage to output  $G_{vg}(s)$ , and the output current to output

Figure 2.3: Simplified System Diagram

Figure 2.4: Generalized Power System Model

voltage, or open loop output impedance  $Z_{out}(s)$ . Additional transfer functions will be derived in the section, such as the control to inductor current  $G_{id}(s)$ , output current to inductor current  $G_{ii}(s)$ , and the input voltage to inductor current  $G_{ivg}(s)$ . These transfer functions will be utilized in following chapters.

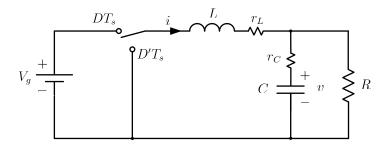

Using the state space analysis approach, the complete set of transfer functions will be derived for the buck converter shown in Figure 2.5.

#### $G_{vd}(s)$ Analysis

To analyze the small signal control to output transfer function of the buck converter, an output load change is modeled with a current source, as shown in Figure 2.5. In terms of the state space analysis, this additional source will be modeled as another input variable to the system.

Figure 2.5: Buck Converter Circuit with Non-Ideal Circuit Elements

Listed below are the fundamental equations for state space analysis. x defines the state variables of the system and the u variables define the inputs. The number of states is defined by the number of storage elements in the system. For the buck converter, there are two states. The output voltage of the converter is the voltage across the capacitor and the corresponding parasitic resistance.

$$x = \begin{bmatrix} i \\ v \end{bmatrix}$$

$$u = \begin{bmatrix} v_g \\ i_o \end{bmatrix}$$

$$\dot{x} = Ax + Bu$$

$$y = Cx + Eu$$

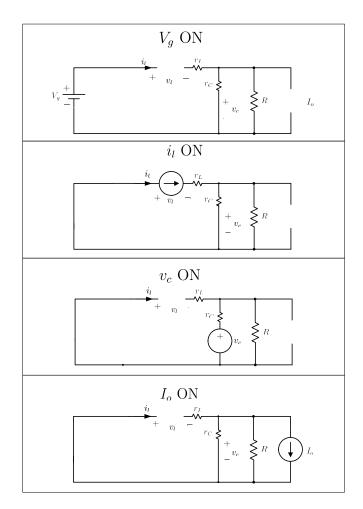

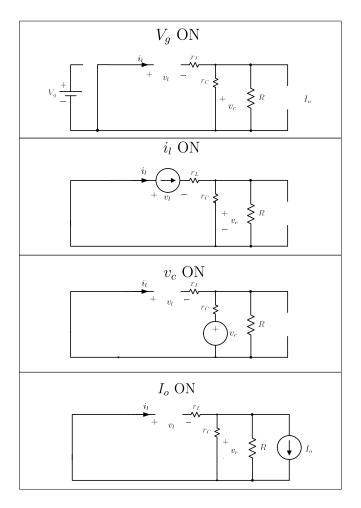

Applying the principles of superposition to the buck converter, the capacitor current and inductor voltage equations are found and summarized below for both switch positions.

During DTs,

$$L\frac{di_{L}}{dt} = -(r_{l} + r_{c} || R)i_{L} - \frac{R}{R + r_{c}}V_{c} + V_{g} + I_{o}(R || r_{c})$$

$$C\frac{dV_{c}}{dt} = \frac{R}{R + r_{c}}i_{L} - \frac{1}{R + r_{l}}V_{c} + 0V_{g} - \left(\frac{R}{R + r_{c}}\right)I_{o}$$

$$V_{out} = (r_{c} || R)i_{L} + \frac{R}{R + r_{c}}V_{c} + 0V_{g} - (R || r_{c})I_{o}$$

Figure 2.6: Buck Converter Superposition Analysis: DTs

During D'Ts,

$$L\frac{\mathrm{d}i_{L}}{\mathrm{d}t} = -(r_{l} + r_{c} || R)i_{L} - \frac{R}{R + r_{c}}V_{c} + 0V_{g} + I_{o}(R || r_{c})$$

$$C\frac{\mathrm{d}V_{c}}{\mathrm{d}t} = \frac{R}{R + r_{c}}i_{L} - \frac{1}{R + r_{l}}V_{c} + 0V_{g} - \left(\frac{R}{R + r_{c}}\right)I_{o}$$

$$V_{out} = (r_{c} || R)i_{L} + \frac{R}{R + r_{c}}V_{c} + 0V_{g} - (R || r_{c})I_{o}$$

With the circuit defined over the two subintervals, the A, B, C, and E matrices can be defined as shown below:

Figure 2.7: Buck Converter Superposition Analysis: D'Ts

$$A_{1} = A_{2} = A = \begin{bmatrix} -\frac{(r_{c} || R + r_{l})}{L} & -\frac{R}{(R + r_{c})L} \\ \frac{R}{(r_{c} + R)C} & -\frac{1}{(r_{c} + R)C} \end{bmatrix}$$

$$B_{1} = \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix}$$

$$B_{2} = \begin{bmatrix} 0 \\ 0 \end{bmatrix}$$

$$B_{2} = \begin{bmatrix} 0 \\ 0 \end{bmatrix}$$

$$B = \begin{bmatrix} \frac{D}{L} \\ 0 \end{bmatrix}$$

$$C_1 = C_2 = C = \begin{bmatrix} (r_c || R) & \frac{R}{R + r_c} \end{bmatrix}$$

$E_1 = E_2 = E = \begin{bmatrix} 0 & -(r_c || R) \end{bmatrix}$

With the state space matrices defined, the control to output transfer function can be calculated as  $G_{vd}(s) = C(sI-A)^{-1}Bd + Ed$ , where  $B_d = (A_1 - A_2)X + (B_1 - B_2)U$  and  $E_d = (C_1 - C_2)X + (E_1 - E_2)U$ . Applying basic matrix manipulation techniques,  $G_{vd}(s)$  is calculated below.

$$X = -A^{-1}BU = \begin{bmatrix} \frac{DVg}{R+r_l} - Io\left(\frac{R^2}{(R+r_c)(R+r_l)} - \frac{Rr_c}{(R+r_c)(R+r_l)}\right) \\ I_o\left(\frac{R^2r_c}{(R+r_c)(R+r_l)} + \frac{R(Rr_c+Rr_l+r_cr_l)}{(R+r_c)(R+r_l)}\right) + \frac{DRV_g}{R+r_l} \end{bmatrix}$$

$$B_d = (A_1 - A_2)X + (B_1 - B_2)U = \begin{bmatrix} \frac{V_g}{L} \\ 0 \end{bmatrix}$$

$$E_d = (C_1 - C_2)X + (E_1 - E_2)U = 0$$

$$G_{vd}(s) = C(sI - A)^{-1}Bd + Ed = \frac{V_g \left(1 + sRC\right)}{\frac{r_c + R}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_c r_l}{R}\right)C\right) + \frac{(R + r_l)}{R}}$$

#### $G_{ii}(s)$ Analysis

When calculating the output load to inductor current transfer function, it can be noticed that the inductor voltage and capacitor current equations will be identical to those used in calculating  $G_{vd}(s)$  above. Using this fact, only the output equation is needed to be derived to find the C and E matrices.

$$y = i$$

$$C_1 = C_2 = C = \begin{bmatrix} 1 & 0 \end{bmatrix}$$

$$E_1 = E_2 = E = \begin{bmatrix} 0 & 0 \end{bmatrix}$$

Using the values found above, the output load to inductor current function is equal to  $G_{ii}(s) = -(C(sI - A)^{-1}B + E)$ , with the negative sign due to the defined current direction.

$$G_{ii}(s) = C(sI - A)^{-1}B + E = \frac{\left(\frac{R - r_c}{R + r_l} + sr_cC\right)}{\frac{r_c + R}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + \frac{r_c}{R}\right)\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \frac{(R + r_l)}{R}\right)$$

$G_{id}(s), G_{vv_g}(s), \text{ and } G_{iv_g}(s)$  Analysis

To calculate  $G_{id}(s)$ , the control to inductor current transfer function,  $G_{vv_g}(s)$ , the input voltage to output voltage transfer function and  $G_{iv_g}(s)$ , the input voltage to inductor current transfer function, the same parameters derived above can be used to solve each equation.

$$G_{id}(s) = C(sI - A)^{-1}Bd + Ed = \frac{V_g}{R} \frac{(1 + s(R + r_c)C)}{\frac{r_c + R}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}}$$

$$G_{vv_g}(s) = C(sI - A)^{-1}B + E = \frac{D(1 + sr_cC)}{\frac{r_c + R}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}}$$

$$G_{iv_g}(s) = C(sI - A)^{-1}B + E = \frac{\frac{D}{R}\left(1 + s\left(R + r_c\right)C\right)}{\frac{r_c + R}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + r_c + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \left(r_l + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \frac{r_cr_l}{R}\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \frac{r_cr_l}{R}\right)C\right) + \frac{(R + r_l)}{R}s^2LC + s\left(\frac{L}{R} + \frac{r_cr_l}{R}\right)$$

#### $Z_o(s)$ Analysis

To calculate the output impedance of the Buck converter, it is possible to use state space analyses techniques. However, due to the input voltage connection of the Buck converter we can take advantage of the fact that the impedance of the buck on the output looks the same regardless of the switch location.

Figure 2.8: Ideal Buck Converter Circuit

$$Z_o(s) = SL \|\frac{1}{sC}\|R = \frac{sL}{1 + s\frac{L}{R} + s^2LC}$$

Figure 2.9: Buck Converter Circuit with Non-Ideal Circuit Elements

One way to incorporate losses into the impedance function is to replace the energy storage element in the impedance equation with the sum of the element and its non-ideal resistive component. Starting with the inductor, every instance of sL is replaced with  $sL + r_l$  in  $Z_o(s)$ .

$$Z_o(s) = \frac{sL + r_l}{1 + \frac{r_l}{R} + s\left(\frac{L}{R} + r_lC\right) + s^2LC}$$

Assuming  $\frac{r_l}{R} << 1$

$$Z_o(s) = \frac{sL + r_l}{1 + s\left(\frac{L}{R} + r_lC\right) + s^2 LC}$$

Now, adding the ESR of the capacitor:

$$sC \Rightarrow \frac{sC}{1+SR_c}$$

$$Z_o(s) = \frac{(sL+r_l)\left(1+sr_cC\right)}{1+s\left(\frac{L}{R}+\left(r_l+r_c\right)C\right)+s^2\left(1+\frac{r_c}{R}\right)LC}$$

The complete output impedance of the Buck converter is found to be:

$$Z_o(s) = \frac{r_l \left(1 + s\frac{L}{r_l}\right) \left(1 + sr_cC\right)}{1 + s\left(\frac{L}{R} + \left(r_l + r_c\right)C\right) + s^2LC}$$

Assuming  $\left(\frac{r_c}{R} << 1\right)$ .

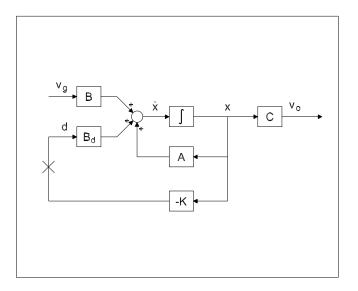

To summarize the results of this section, Figure 2.10 shows the results of the state space analysis for the buck converter presented in this chapter. The results of the analysis will be leveraged throughout the text.

| Buck Converter Transfer Functions                         |                                                                               |                                                                                  |  |  |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|

|                                                           | Ideal Case                                                                    | Losses Included                                                                  |  |  |  |

|                                                           | $Q = \frac{R}{L}\sqrt{LC} \qquad r_l = 0$                                     | $Q = rac{\sqrt{LC}}{(r_c + r_l)C + rac{L}{R}}$ $r_l  eq 0,  rac{r_l}{R} << 1$ |  |  |  |

|                                                           | $\omega_0 = rac{1}{\sqrt{LC}}$ $r_c = 0$                                     | $\omega_0 = rac{1}{\sqrt{LC}} \qquad r_c  eq 0,  rac{r_c}{R} << 1$             |  |  |  |

|                                                           | $\triangle(s) = 1 + \frac{s}{\omega_0 Q} + \left(\frac{s}{\omega_0}\right)^2$ |                                                                                  |  |  |  |

| $G_{vd} \triangleq \frac{\hat{v}}{\hat{d}}$               | $rac{V_g}{	riangle(s)}$                                                      | $\frac{V_g(1+sr_cC)}{\triangle(s)}$                                              |  |  |  |

| $G_{vvg} \triangleq \frac{\hat{v}}{\hat{v_g}}$            | $rac{D}{	riangle(s)}$                                                        | $\frac{D(1+sr_cC)}{\triangle(s)}$                                                |  |  |  |

| $Z_{out} = G_{vi_o} \triangleq \frac{\hat{v}}{\hat{i_o}}$ | $rac{sL}{	riangle(s)}$                                                       | $\frac{r_l \left(1 + \frac{sL}{R}\right) (1 + sr_c C)}{\triangle(s)}$            |  |  |  |

| $G_{id} \triangleq \frac{\hat{i}}{\hat{d}}$               | $\frac{\frac{Vg}{R}}{\bigtriangleup(s)}$                                      | $\frac{\frac{V_g}{R}(1{+}sRC)}{\triangle(s)}$                                    |  |  |  |

| $G_{iv_g} \triangleq \frac{\hat{i}}{\hat{v_g}}$           | $rac{rac{D}{R}(1+sRC)}{	riangle(s)}$                                        | $\frac{\frac{D}{R}(1{+}sRC)}{\triangle(s)}$                                      |  |  |  |

| $G_{ii_0} \triangleq \frac{\hat{i}}{\hat{i_0}}$           | $rac{1}{	riangle(s)}$                                                        | $\frac{(1+sr_cC)}{\triangle(s)}$                                                 |  |  |  |

Figure 2.10: Summary of Plant Transfer Functions

#### 2.3 Pulse-width Modulator

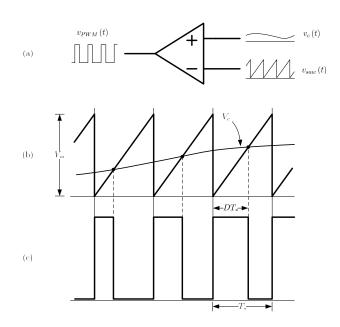

With a complete model in place for the Buck regulator, the next item in the system diagram to derive is the pulse-width modulator.

From inspection of Figure 2.11, it can be approximated that the duty cycle can be represented by the following relationship:

$$d(t) = \frac{V_c(t)}{V_M} \text{ for } 0 \le V_c(t) \le V_M$$

Rearranging,  $\frac{d(t)}{V_c(t)} = \frac{1}{V_M}$ . For a complete derivation confirming the PWM conversion gain can be approximated to this equation, refer to the analysis presented in [?].

Figure 2.11: PWM Conversion Diagram

#### 2.4 Summary

Now that the basic system has been defined, the final block to be derived in the Buck converter system model is the compensator,  $G_c(s)$ . The compensator will be the primary topic of the next several chapters, as it will be leveraged to improve the closed-loop performance of the derived buck regulator system. The equations in this chapter will be heavily leveraged in the remainder of the text.

16

### Bibliography

- [1] M. Xu K. Yao and F. Lee. Design considerations for vrm transient response based on the output impedance. *IEEE*, 18(6):1270–1277, November 2003.

- [2] M. Xu K. Yao, K. Lee and F. Lee. Optimal design of the active droop control method for the transient response. *IEEE*, pages 718–723, 2003.

- [3] RD Middlebrook. Predicting modulator phase lag in pwm converter feedback loops. *Powercon*, 1981.

BIBLIOGRAPHY

Chapter 3

### **Bode Plots**

Introduction

|H(s)| —— A

H(s) $0^{o}$

Figure 3.1: Simple Gain

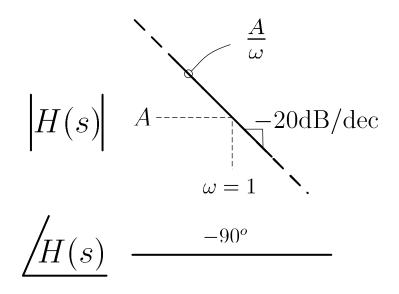

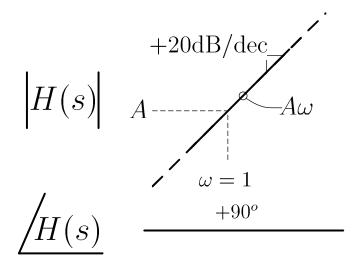

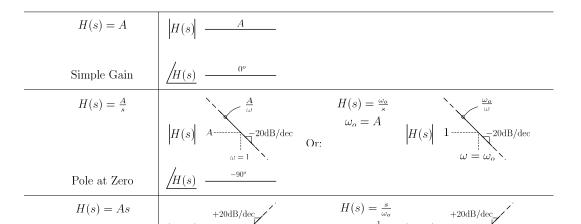

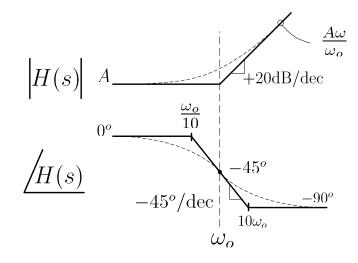

Figure 3.2: Pole at Zero

Figure 3.3: Zero at Zero

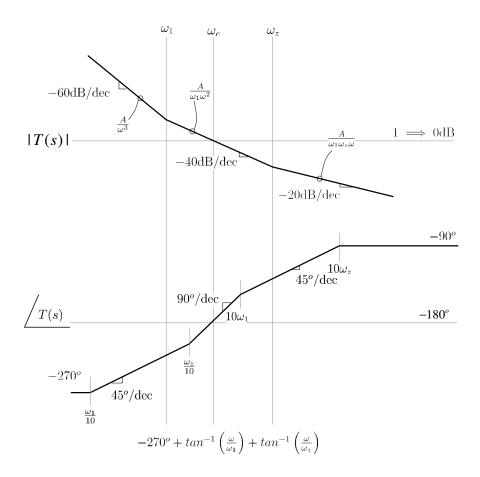

#### 3.0.1 Bode Plots

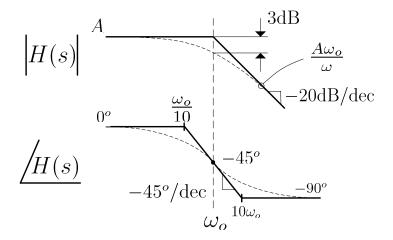

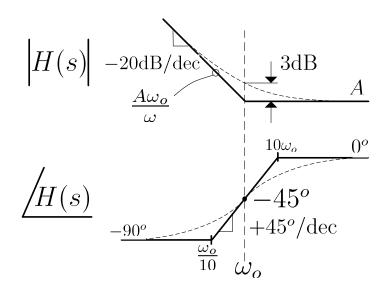

Figure 3.4: Pole at  $\omega_o$

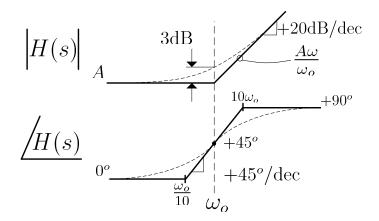

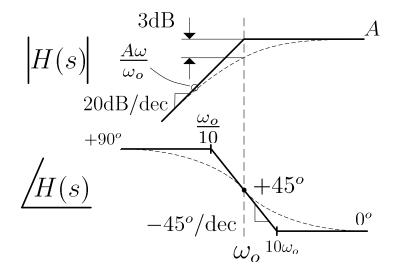

Figure 3.5: Zero at  $\omega_o$

Figure 3.6: Right Half Plane Zero at  $\omega_o$

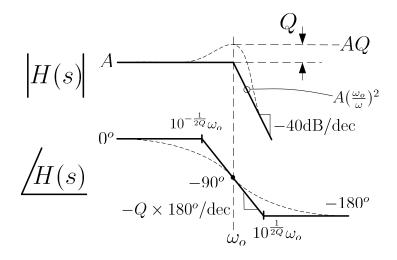

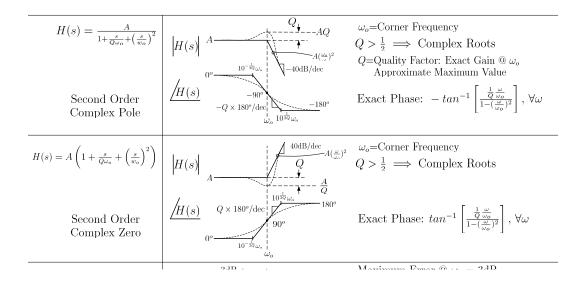

Figure 3.7: Second Order Complex Pole at  $\omega_o$

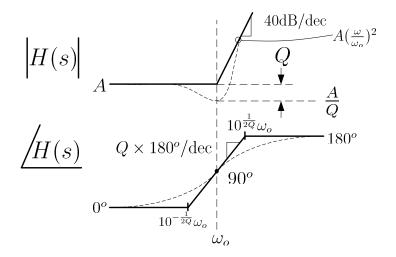

Figure 3.8: Second Order Complex Zero at  $\omega_o$

Figure 3.9: Inverted Pole at  $\omega_o$

Figure 3.10: Inverted Zero at  $\omega_o$

26

### Chapter 4

### Single Loop Voltage Mode Control

This paper develops a buck converter design example using different compensation methods to ensure closed loop stability and to optimize system performance. Various compensators are designed using asymptotic Bode plots based primarily on loop bandwidth and stability margins. Computer simulation results are included to show time domain step response behavior and to verify performance improvements.

#### 4.1 Introduction

The buck converter is a switch mode, DC-DC, power supply. It accepts a source voltage,  $V_g$  and produces a lower output voltage, V with high efficiency. An important component of a practical buck converter is control feedback which assures a constant output voltage and attenuates unwanted disturbances. The feedback loop of a buck converter presents several challenges which are explored in the compensation examples.

In this paper we present a series of example buck converter feedback compensation approaches. The design of the buck converter circuit is kept constant to allow comparison of the effects of different compensation schemes. The primary tool that will be applied to evaluate the different compensation approaches are asymptotic Bode plots which are drawn based on corner frequencies of each block in the regulator system. This methodology provides a quick and efficient assessment of circuit performance and an intuitive sense for the trade offs for each compensation approach. Bode plots also directly illuminate the two critical loop stability characteristics, gain and phase margin (GM and PM respectively).

Additional analysis of each compensation approach is undertaken through computer simulation. The PECS [1] circuit simulator is used to evaluate the effects of  $V_g$  transients, a common problem in real power supply designs. A Matlab [2] simulation is also performed to validate the manual Bode analysis and to determine the exact gain and phase margin. Finally a closed loop Matlab simulation is used to show the ability of the feedback system to attenuate undesired effects as a function of frequency.

#### 4.2 Buck Converter System Models

#### 4.2.1 General Model

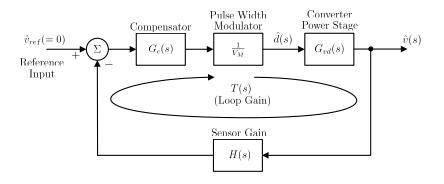

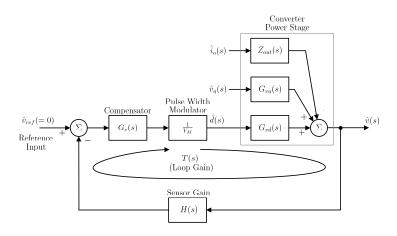

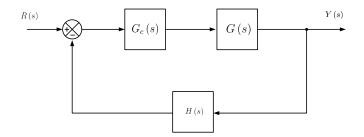

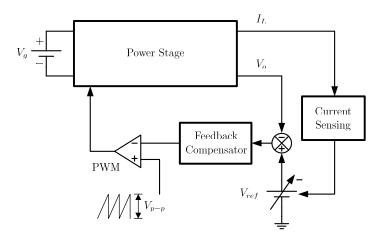

Figure 4.1 is a block diagram of the system components of a buck converter with feedback. The converter power stage accepts  $V_g$  as its power source and the control input d(s) to produce the output voltage V. The feedback sensor H(s), monitors the converter output voltage which is then compared with a reference voltage  $V_{ref}$ . The difference output of these two voltages is provided to the feedback compensation circuit  $G_c(s)$  and then to the pulse width modulator (PWM) which produces the control waveform for the switching converter d(s). The resulting loop gain is thus given by

$$T(s) = G_c(s) \left(\frac{1}{V_M}\right) G_{vd}(s) H(s)$$

(4.1)

Figure 4.1: Generalized Power System Model

#### 4.2.2 Simplified System Model

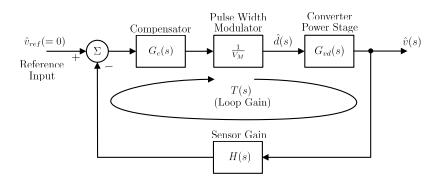

The general buck converter block diagram provides a complete model for analysis of converter. However, for our analysis we will use a simplified model show in Fig. 4.2 which includes only the elements required for the analysis we will provide. We do not evaluate any source of disturbance except  $V_q$  transients.

Figure 4.2: Simplified System Diagram

#### 4.2.3 Design Targets

To facilitate easy comparison between the selected compensation schemes, the design of the buck converter is fixed with specified values. These values are specified in Table 4.1.

| Table 4.1: Specified values |                   |                      |

|-----------------------------|-------------------|----------------------|

| Name                        | Value             | Description          |

| $V_g$                       | 28V               | Input Voltage        |

| V                           | 15V               | Output Voltage       |

| Iload                       | 5A                | Load current         |

|                             | $50 \mathrm{uH}$  | Buck inductor value  |

| C                           | $500 \mathrm{uF}$ | Buck capacitor value |

| $V_m$                       | 4V                | PWM ramp amplitude   |

| H(s)                        | 1/3               | Sensor gain          |

| $f_s$                       | 100kHz            | PWM frequency        |

Table 4.1: Specified values

#### 4.2.4 Buck Converter Model Analysis

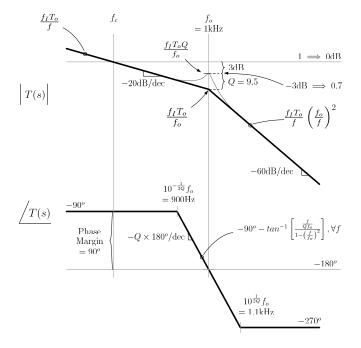

Figure 4.3 shows a schematic model for the power converter block. The LCR is a second order circuit with a transfer function described by equation (4.2). It has a resonant frequency value,  $\omega_o = 6.28 \text{k} \text{ rad/s}$  or  $f_o(=\frac{\omega_o}{2\pi}) = 1.0 \text{ kHz}$  from (4.3) and a Q of 9.5 from (4.4). The low frequency gain of the converter is equal to  $V_g$  which is specified to be 28V.

$$G_{vd}(s) = V_g \frac{1}{1 + \frac{s}{Q\omega_0} + \left(\frac{s}{\omega_0}\right)^2}$$

(4.2)

$$\omega_o = \frac{1}{\sqrt{LC}} \tag{4.3}$$

Figure 4.3: Converter Power Stage

$$Q = R\sqrt{\frac{C}{L}} \tag{4.4}$$

Consider the transfer function  $v(s)/v_d(s)$  of the low pass filter formed by the LCR network. The switching frequency  $f_s = 100$ kHz is much higher than the resonant frequency  $f_0 = 1$ kHz of the LCR network. During circuit operation, the switch toggles the LCR input between  $V_g$  and ground with a duty cycle D determined by the feedback loop. A Fourier analysis of the LCR input waveform includes an average DC component  $V = DV_g$  and an  $f_s$  fundamental component and its harmonics as typified by a rectangular waveform. The LCR acts as a low pass filter with a cut off frequency equal to  $f_o$ . It passes the DC component to the output but attenuates  $f_s$  and its harmonics.

## 4.3 Uncompensated System

It is instructive to start our evaluation with an uncompensated open loop converter, one with a  $G_c(s) = 1$ . The loop gain is then given from (4.1) as

$$T(s) = \frac{T_o}{1 + \frac{s}{Q\omega_0} + \left(\frac{s}{\omega_o}\right)^2}$$

(4.5)

where

$$T_o = \frac{V_g H(0)}{V_m} \tag{4.6}$$

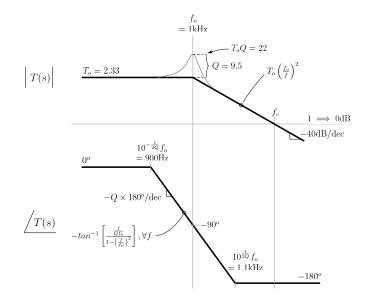

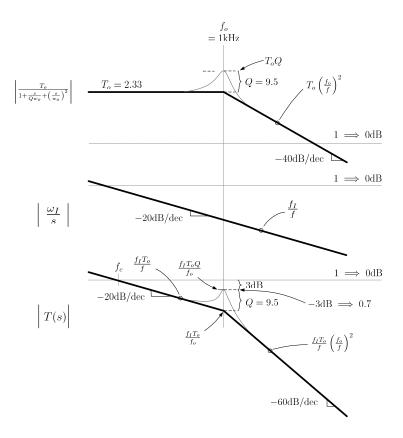

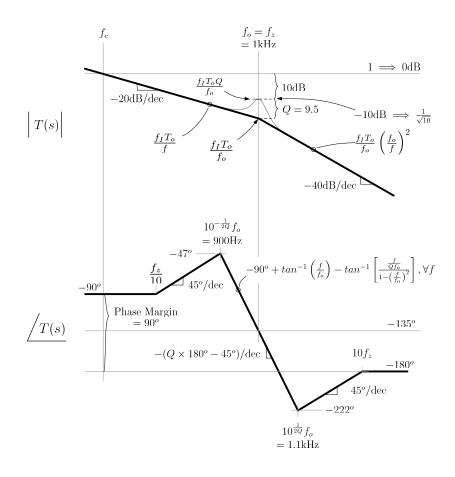

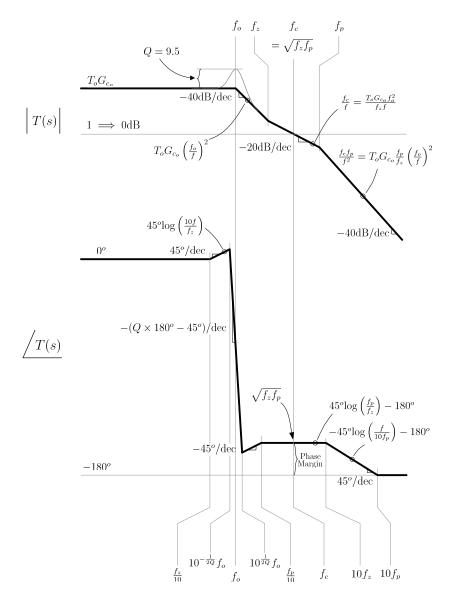

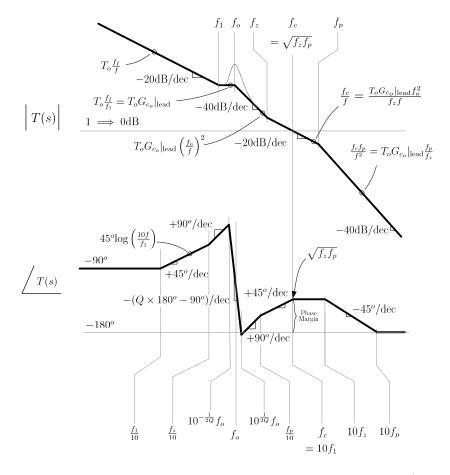

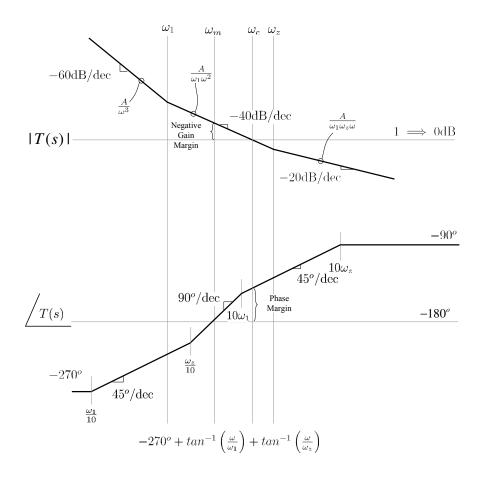

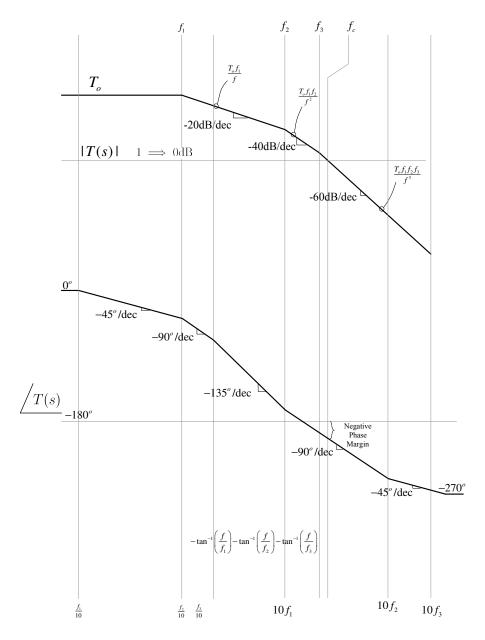

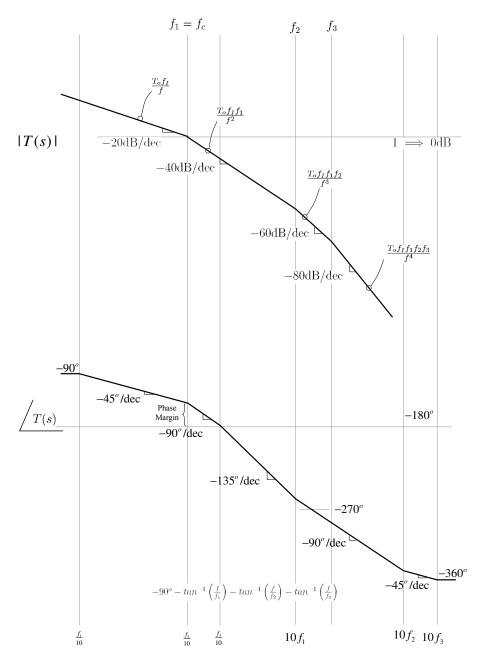

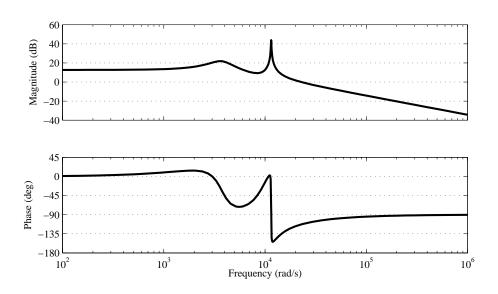

To construct a Bode plot we use the values from equations (4.2)-(4.4) to establish the shape of the Bode magnitude plot. The low frequency gain given by (4.6) has a value of 2.33. The magnitude around  $f_o$  peaks due to the resonant Q of 9.5. At frequencies above  $f_o$  the gain declines at -40dB/decade.

#### 4.3. UNCOMPENSATED SYSTEM

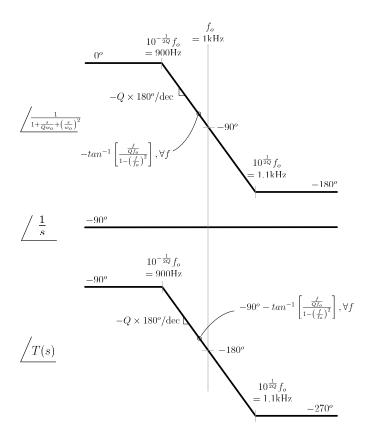

The Bode phase plot is determined only by  $G_{vd}(s)$ . It has a low frequency phase shift of 0°. At  $f_o 10^{-\frac{1}{2Q}}$  or 886Hz ( $\approx$  900Hz), the phase turns negative and at  $f_0$  the phase has reached  $-90^{\circ}$ . The phase continues to become more negative until it reaches  $-180^{\circ}$  at  $10^{\frac{1}{2Q}}$  or 1129Hz ( $\approx$  1.1kHz). At frequencies higher than 1.1kHz the phase remains at  $-180^{\circ}$ .

Figure 4.4: Uncompensated Gain and Phase Plot

From the Bode plot it can be determined that unity gain occurs at a frequency,  $f = f_c$  such that

$$T_o \left(\frac{f_o}{f_c}\right)^2 = 1 \tag{4.7}$$

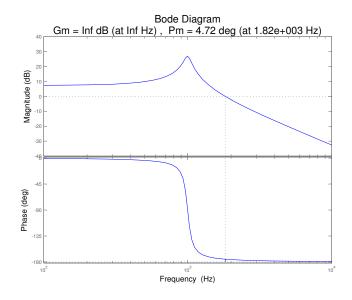

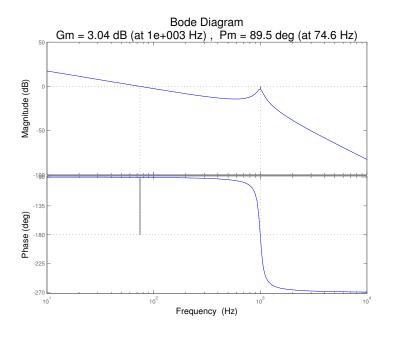

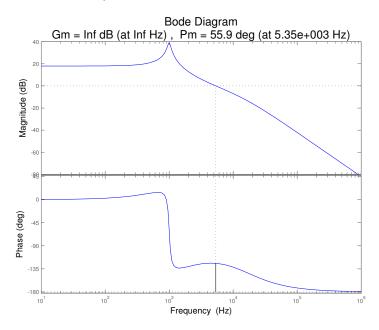

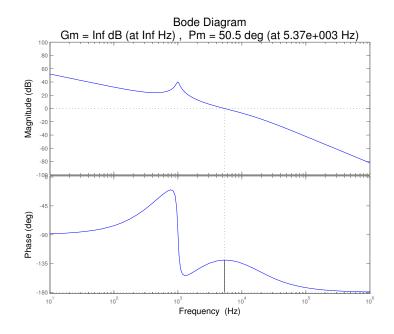

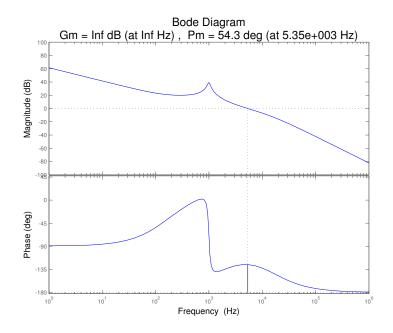

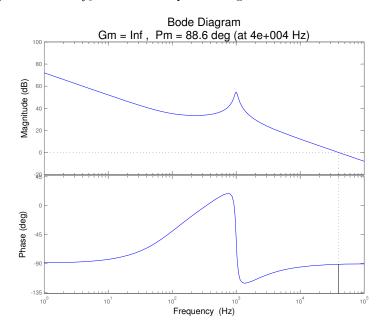

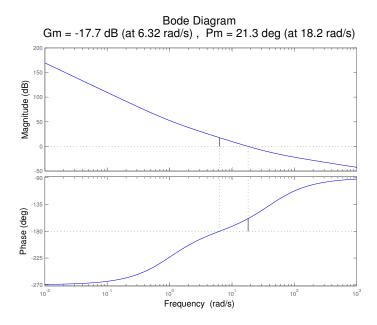

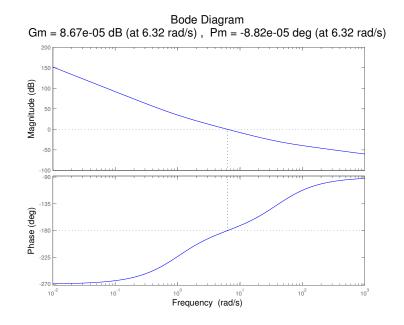

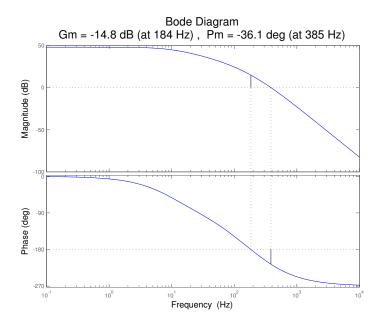

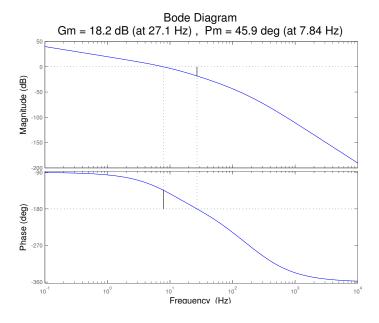

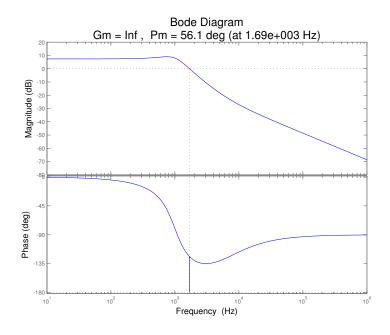

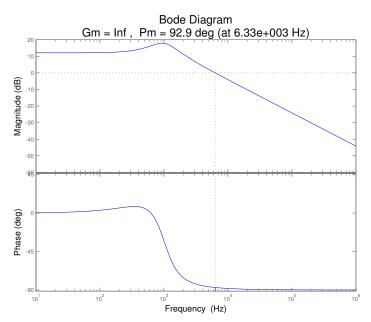

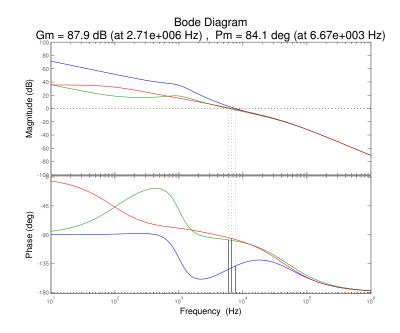

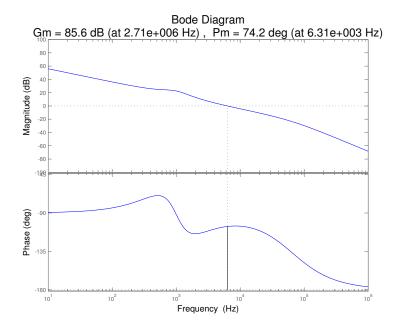

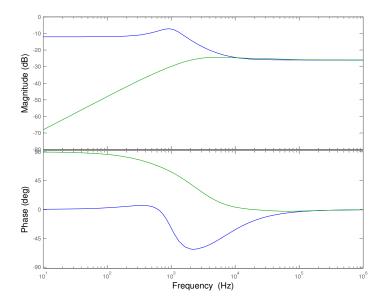

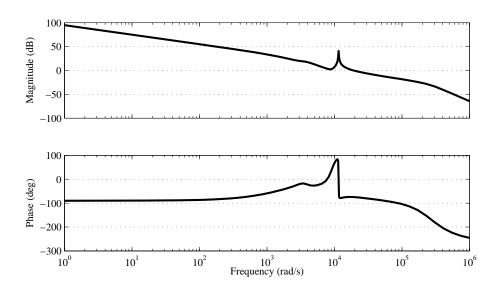

which with  $T_o=2.33$  and  $f_o=1$ kHz, results in  $f_c=1.5$ kHz. At this frequency the phase is  $-180^{\circ}$  providing zero phase margin. The phase asymptotes show that phase does not cross the  $-180^{\circ}$  phase level (but is asymptotic to it) which implies that the gain margin is infinite. Figure 4.5 is a Matlab margin plot indicating the actual unity gain frequency to be 1.8 kHz with a phase margin of 4.7°. Also, the Matlab analysis indicates an infinite gain margin.

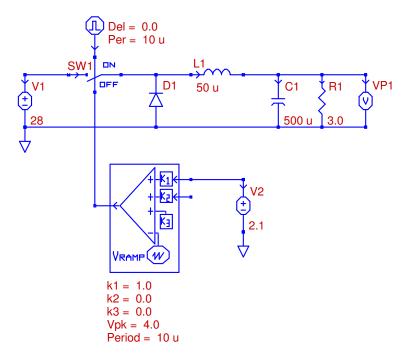

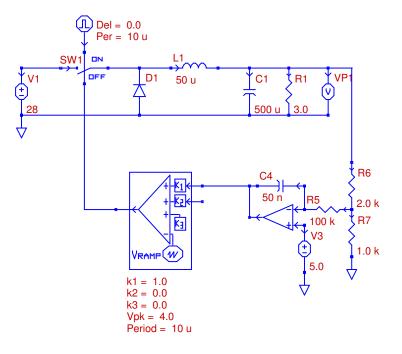

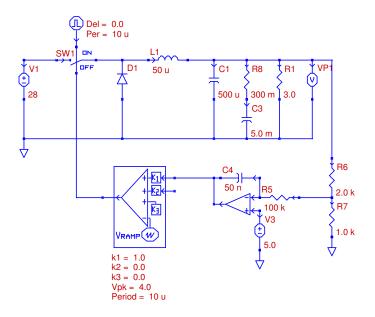

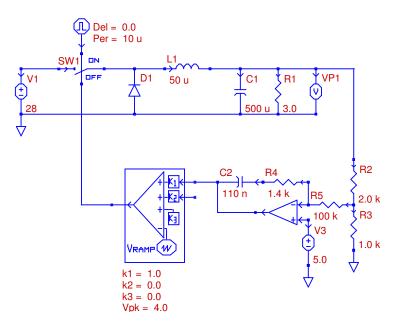

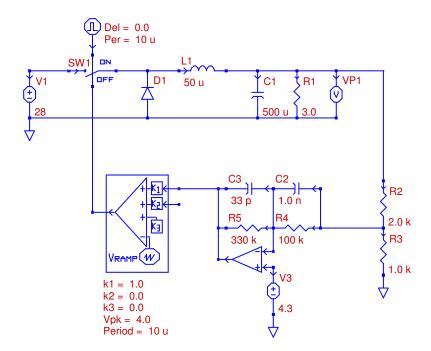

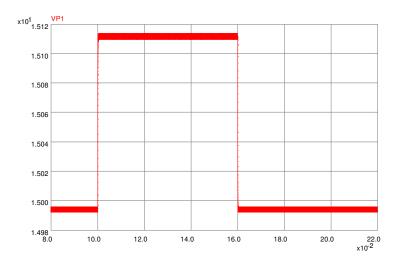

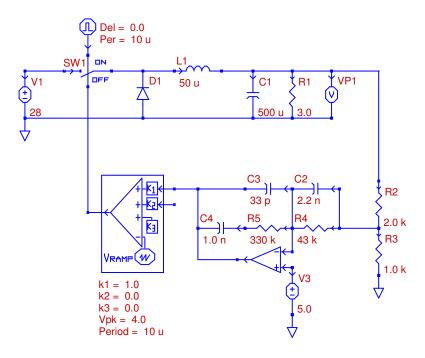

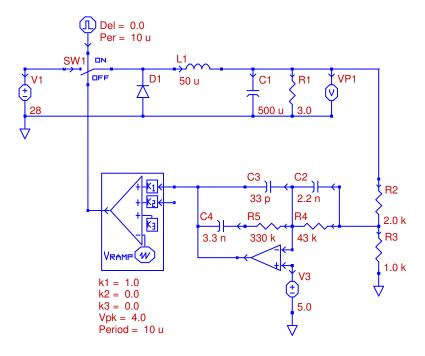

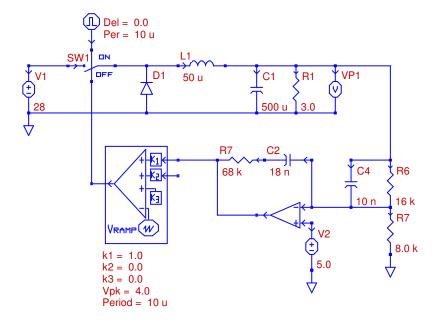

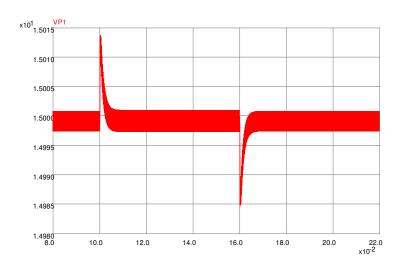

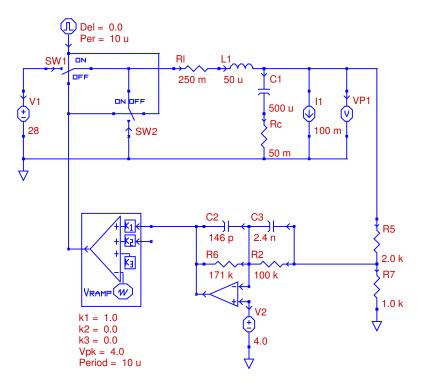

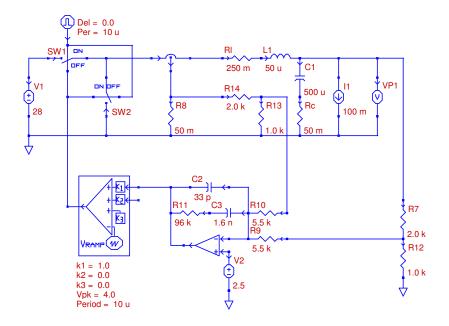

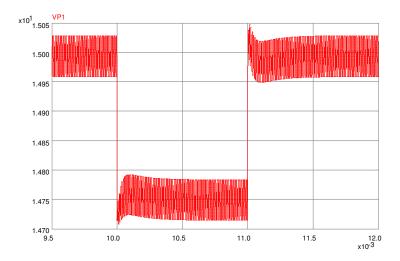

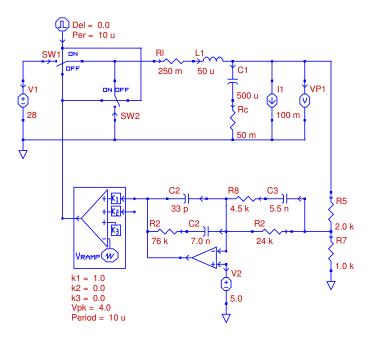

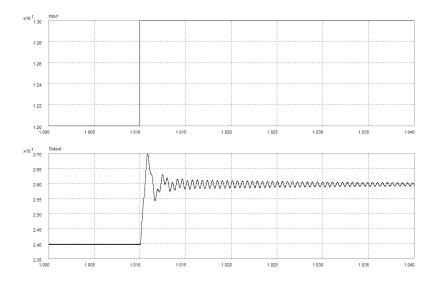

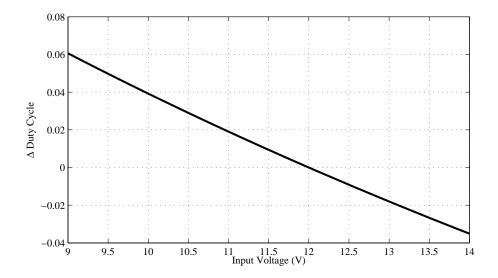

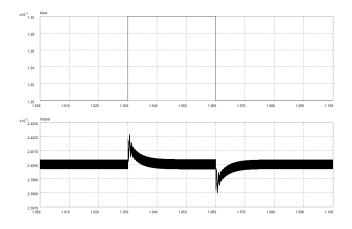

Figure 4.6 shows a PECS implementation of the open loop buck converter system. The input to the modulator is set to 2.1V which results in the target

Figure 4.5: Matlab Uncompensated Bode plot

steady state duty ratio of  $D = \frac{V}{V_g} = \frac{15}{28} = 0.54$  required to set the output voltage at V = 15V for a nominal input voltage of  $V_g = 28$ V.

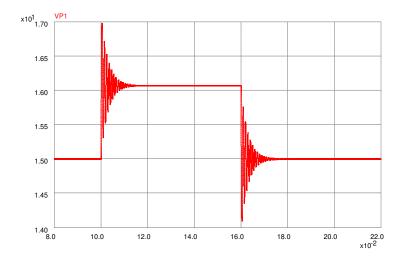

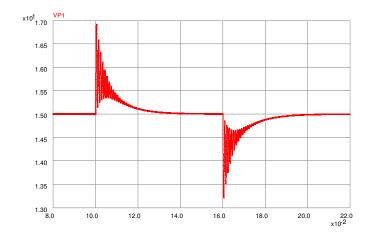

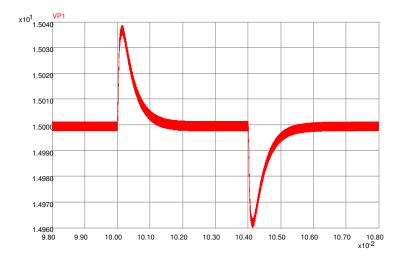

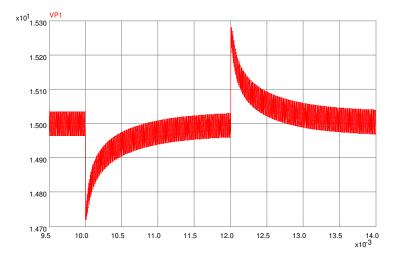

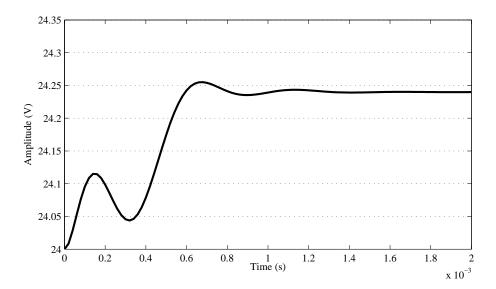

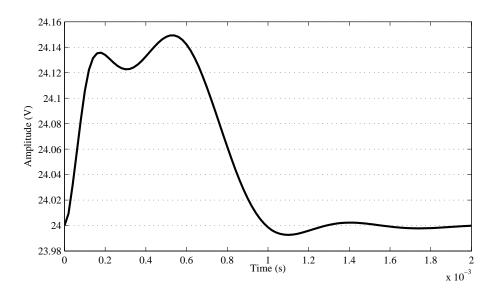

Figure 4.7 shows the output voltage response of the open loop system shown in Figure 4.6 for voltage steps in  $V_g$  of  $28V \rightarrow 30V \rightarrow 28V$ . The response is indicative of the high resonance Q of 9.5 at the resonant frequency  $f_o=1$ kHz. Note also that at an input voltage of  $V_g=30$ V the output voltage settles at  $V = DV_g = 0.54 \times 30 = 16.2$ V, as shown in Fig. 4.7.

Figure 4.6: PECS Schematic of Open Loop System

Figure 4.7: PECS Simulation of Open Loop System

## 4.4 Dominant Pole Compensation

Dominant pole compensation is one of the simplest and most common forms of feedback compensation. The motivating idea behind this type of feedback control is to shape the open loop gain of the system such that two objectives are achieved:

- 1. High gain is achieved at DC and low frequencies. This condition ensures low steady state error.

- 2. The gain at the plant's lowest frequency pole is less than or equal to 0dB. This condition ensures a positive phase margin and, consequently, stability.

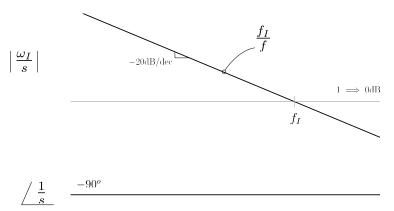

In the case of dominant pole compensation, these objectives are achieved using a compensator consisting of a single pole at a frequency well below those of the plant's poles. For the purposes of this example, an integrator, which is just a pole at DC, is employed

$$G_c(s) = \frac{\omega_I}{s} \tag{4.8}$$

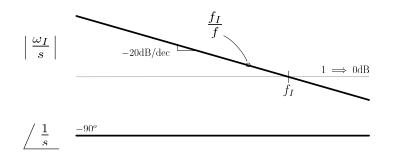

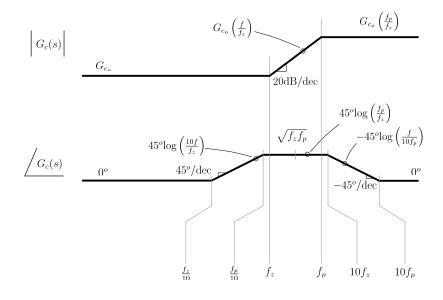

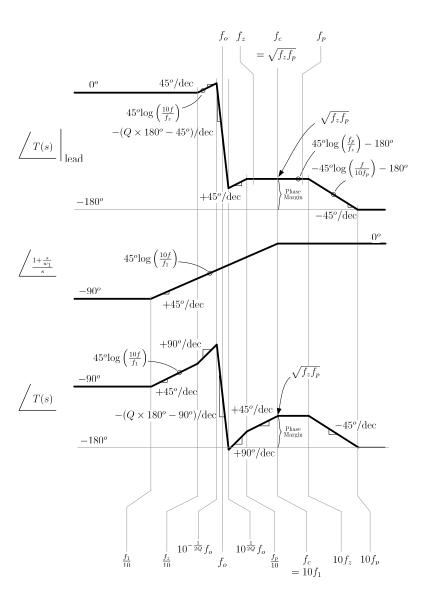

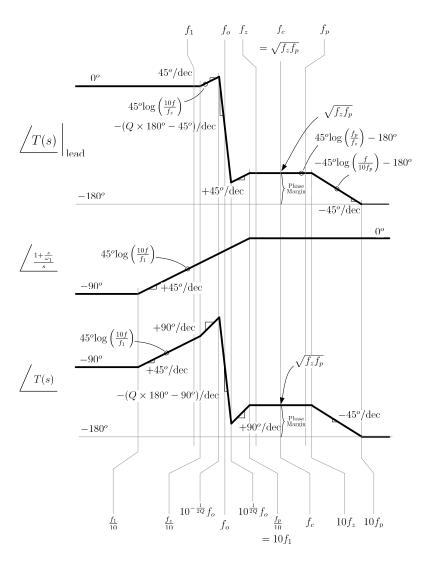

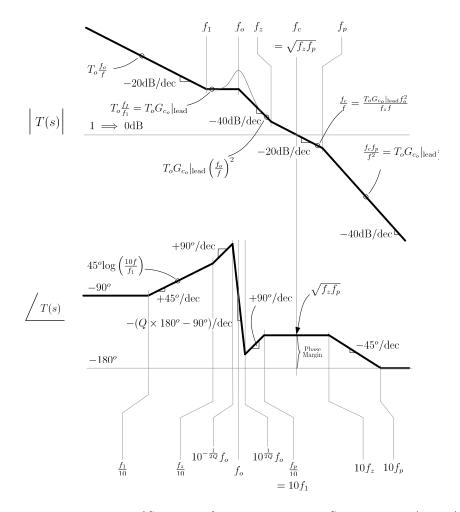

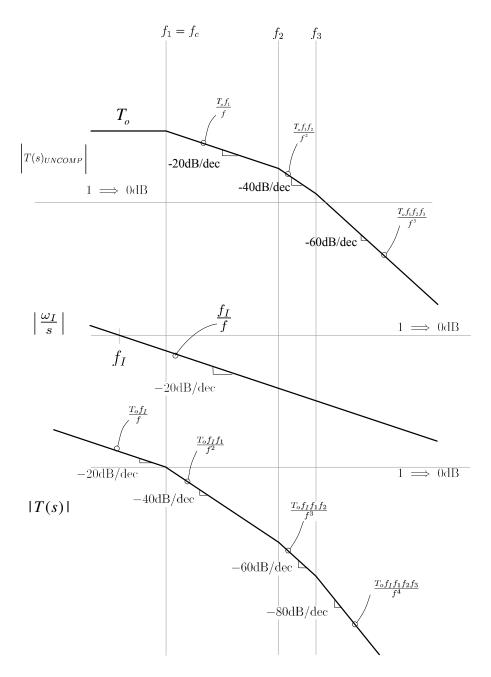

where  $\omega_I (= 2\pi f_i)$  is an appropriately chosen design constant. Figure 4.8 shows the Bode plot asymptotes for the magnitude and phase of this compensator.

Figure 4.8: Bode Plot of Dominant Pole Compensator

Design of the compensator now consists of selecting an appropriate compensator parameter,  $f_I$ . Following the previously stated criteria, this is a matter of choosing the largest compensator gain such that the total gain at the lowest frequency plant pole(s) is less than 0dB. The loop gain of the system with this compensator is given by

$$T(s) = \frac{\omega_I T_o}{s \left[ 1 + \frac{s}{Q\omega_0} + \left(\frac{s}{\omega_0}\right)^2 \right]}$$

(4.9)

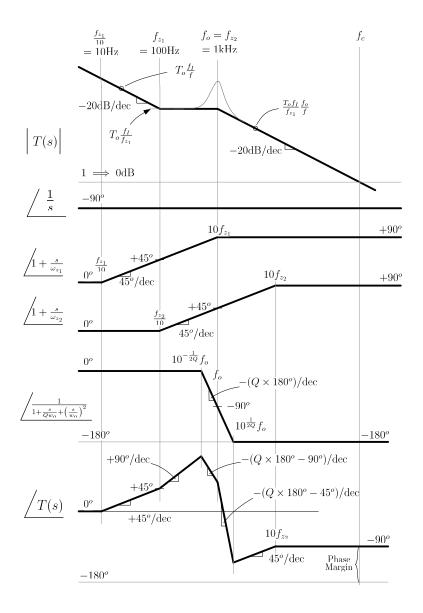

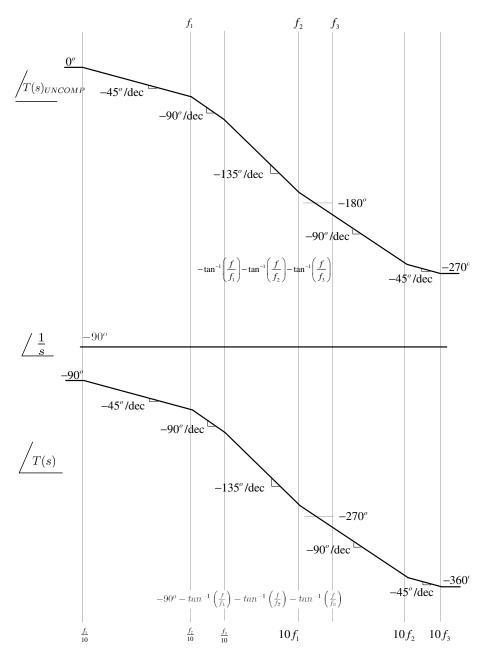

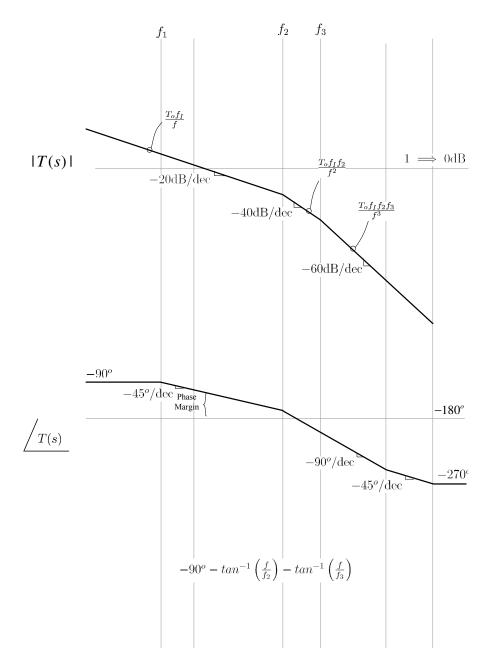

Figure 4.9 shows the graphical construction of the phase asymptotes for the loop gain with the compensator. Note that because the plant's dominant pole is second order, it contributes a phase shift of  $-180^{\circ}$  at high frequencies and a shift of exactly  $-90^{\circ}$  at  $f_o$ . Furthermore, the compensator contributes its own  $-90^{\circ}$  phase shift and does so for all frequencies. Consequently, the total phase shift of the compensated open loop transfer function is  $-180^{\circ}$  at the dominant pole frequency,  $f_o$ . For this reason it is prudent to design in some additional gain margin. A value of 3dB is initially chosen for this analysis.

Figure 4.9: Graphical Construction of Phase Asymptotes for Dominant Pole Compensated Open Loop

Figure 4.10 shows how the plant and compensator transfer functions combine to produce the gain of the compensated open loop. To achieve a loop gain that is -3dB at  $f_o$ , we require the magnitude at  $f_o$  to equal 0.7

$$\frac{f_I T_o Q}{f_o} = 0.7$$

(4.10)

For  $T_o = 2.33$  and  $f_o = 1.0$ kHz, we find  $f_I = 32$ .

Figure 4.10: Graphical Construction of Gain Asymptotes for Dominant Pole Compensated Open Loop

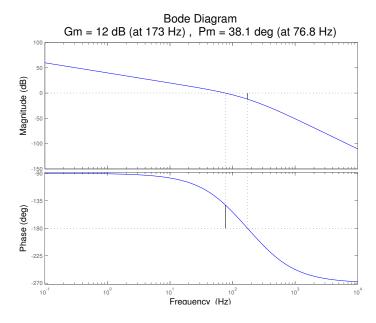

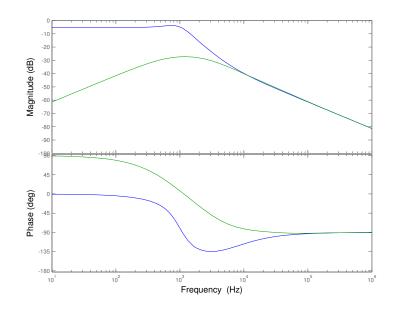

Figure 4.11 shows the Bode plot of the resulting gain and phase asymptotes and Figure 4.12 shows a Matlab margin analysis which confirms the design.

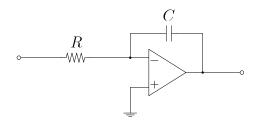

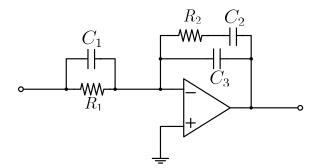

With a compensator designed and verified via Matlab, the next stage is to design a circuit that implements the compensator. Figure 4.13 shows the general

Figure 4.11: Open Loop System Gain and Phase with Dominant Pole Compensation

form of an operational amplifier in a integrator configuration. The transfer function for this circuit is given by:

$$G(s) = \frac{-1}{(s/\omega_o)} \tag{4.11}$$

where

$$\omega_o = \frac{1}{RC} \tag{4.12}$$

where  $\omega_o$  is the frequency at which the integrator gain is unity.

A capacitor value of 50nF is chosen for C. This value is within the range of low-cost, commercially available ceramic capacitors and is small enough to avoid any op-amp slew rate issues. Equating  $\omega_o$  with the compensator parameter,  $\omega_I$  (=  $2\pi f_I$ ) and solving for R gives

$$R = \frac{1}{\omega_I C} = \frac{1}{2\pi (32)(50\text{nF})} \approx 100\text{k}\Omega$$

(4.13)

Figure 4.12: Matlab Analysis of Dominant Pole Compensator

Figure 4.13: Op-Amp Integrator Circuit

A PECS simulation is created to verify the time domain performance of the implementation. Figure 4.14 shows the complete PECS circuit model for the design.

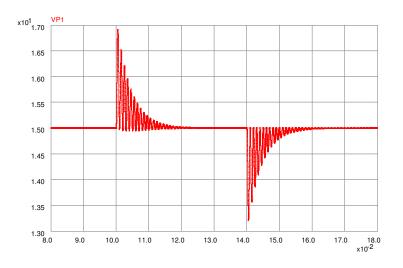

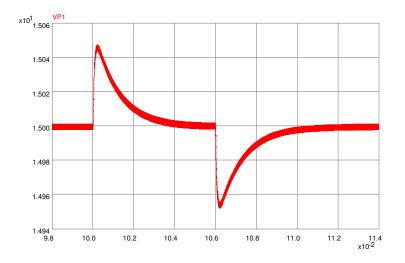

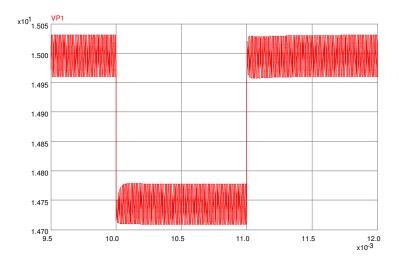

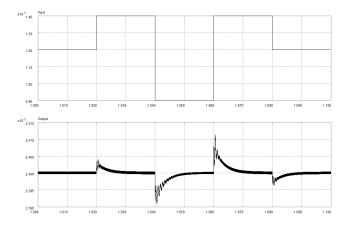

Figure 4.15 shows the results of the PECS simulation for a 2V disturbance on the supply voltage,  $V_g$ . The input voltage steps are  $28V \rightarrow 30V \rightarrow 28V$ . The simulation exhibits several undesirable characteristics:

- 1. The regulator does a poor job of rejecting the input voltage disturbance. Nearly all of the input voltage excursion shows up as a transient on the output.

- 2. The regulator exhibits a substantial amount of ringing in response to the

Figure 4.14: PECS Schematic of Dominant Pole Compensated System

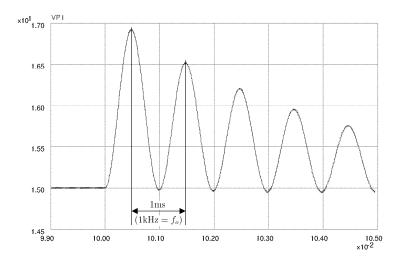

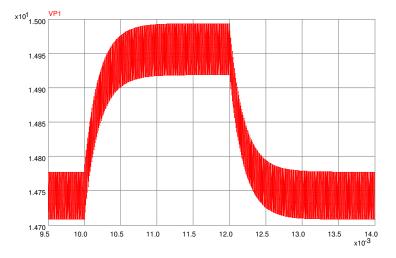

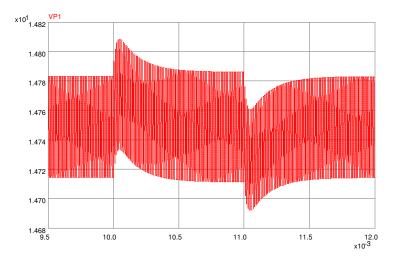

input disturbance. Closer examination of the ringing, as shown in Figure 4.16, reveals that the frequency of the oscillations is the same as the resonant frequency of the plant,  $f_o$ , and is not the result of defective control loop design.

It is clear from the simulation results that, although the design is stable and exhibits zero steady-state error, there is much room for improvement, particularly with respect to its transient response.

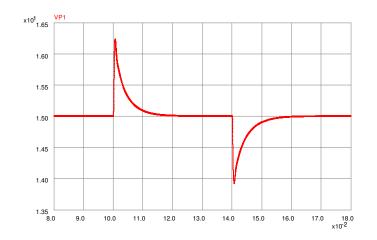

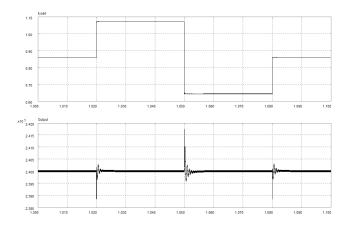

One additional experiment is performed using the dominant pole compensation scheme. The Q of the plant's dominant pole is reduced by placing a large capacitor in series with a small damping resistance. Figures 4.17 and 4.18 show the PECS circuit schematic and simulation results, respectively.

One can see clearly that the ringing of the previous design has been eliminated. Unfortunately, the poor rejection of input voltage transients remains.

Furthermore, this is probably not an ideal solution from a practical standpoint. The large value capacitor will be relatively expensive in terms of com-

Figure 4.15: PECS Simulation of Dominant Pole

Figure 4.16: Pole of Dominant Pole Simulation Showing Oscillation at Resonant Frequency

ponent price and physical space. Alternate compensation schemes still offer the potential for better performance at lower cost.

Figure 4.17: PECS Schematic of Dominant Pole with Damping

Figure 4.18: PECS Simulation of Dominant Pole with Zero Compensation and Damping

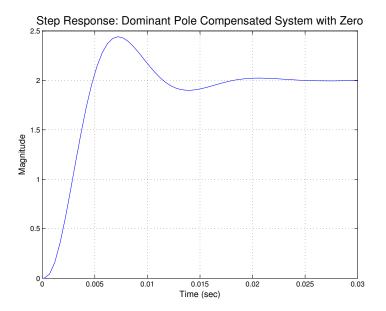

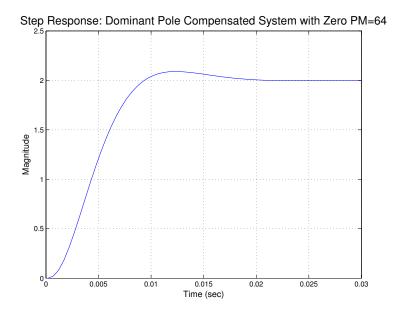

### 4.5 Dominant Pole Compensation with Zero

The dominant pole compensator of the previous section, while stable and having zero steady state error, exhibits several undesirable characteristics including poor rejection of input supply voltage excursions and pronounced ringing in response to transients. One might assume that these issues are related to the minimal, 3dB, gain margin for which the compensator was designed. This section explores that line of reasoning by modifying the compensator of the previous section in order to substantially increase the gain margin.

The dominant pole compensator is modified by adding a zero at the resonant frequency of the plant and by reducing the gain to -10dB. Overall gain margin is improved in two ways:

- 1. by directly increasing the gain margin at the resonant frequency,  $f_o$ , from 3dB to 10dB.

- 2. by shifting the frequency at which the phase reaches  $-180^{\circ}$  beyond the resonant frequency and the gain peak due to the plant's Q.

The form of the modified compensator transfer function is:

$$G_c(s) = \omega_I \frac{1 + s/\omega_z}{s} \tag{4.14}$$

We will use  $\omega_z = \omega_o$  or  $f_z \left(=\frac{\omega_z}{2\pi}\right) = f_o$ . Which results in a loop gain of

$$T(s) = \omega_I \frac{1 + s/\omega_o}{s} \frac{T_o}{1 + \frac{s}{Q\omega_o} + \left(\frac{s}{\omega_o}\right)^2}$$

(4.15)

Figure 4.19 shows the resulting Bode plot asymptotes. We would like to set the gain at  $f_o$  to  $1/\sqrt{10}$  (which corresponds to -10dB). From the magnitude plot we see that we want

$$\frac{f_I T_o Q}{f_o} = \frac{1}{\sqrt{10}}$$

(4.16)

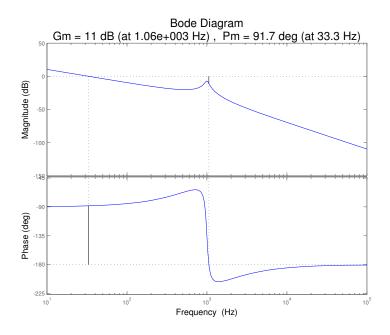

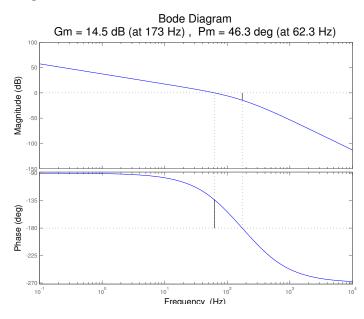

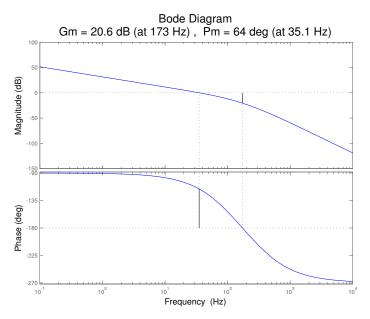

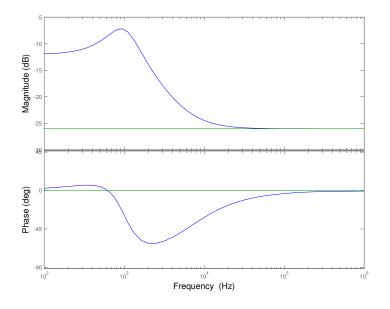

which given  $T_o = 2.33$ , Q = 9.5,  $f_o = 1kHz$ , results in  $f_I = 14.3$ . Figure 4.20 shows a Matlab confirmation of the Bode plot. Note that a gain margin of 11dB is predicted at a phase cross-over frequency of 1.06kHz, slightly higher than the plant's resonant frequency.

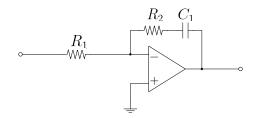

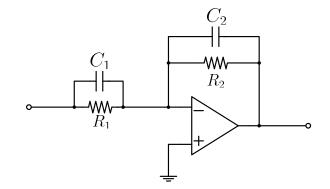

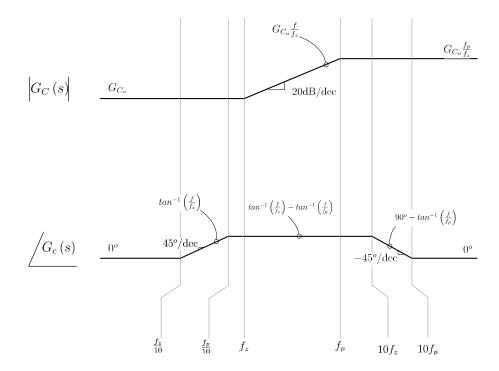

Figure 4.21 shows a standard op-amp implementation with the desired transfer function. The transfer characteristics of the circuit are given by:

$$G(s) = -A \frac{1 + s/\omega_1}{\frac{s}{\omega_1}}$$

(4.17)

where:

Figure 4.19: Open Loop System Gain and Phase with pole-zero Compensation (10dB GM)

$$A = \frac{R_2}{R_1}$$

and  $\omega_1 = \frac{1}{R_2 C_1}$  (4.18)

Equating  $f_1(=\frac{\omega_1}{2\pi})$  to the plant resonant frequency,  $f_o$  and  $\omega_I$  to  $A\omega_1$  provides two equations with three unknowns. Choosing, somewhat arbitrarily, a value of 100k for R1, leads to the following values.

$$R_2 = \frac{f_I R_1}{f_1} = \frac{(14.3)(100 \mathrm{k}\Omega)}{(1\mathrm{k}\Omega)} = 1.4\mathrm{k}\Omega \tag{4.19}$$

$$C_1 = \frac{1}{\omega_1 R_2} = \frac{1}{2\pi (1 \text{kHz})(1.4 \text{k}\Omega)} = 110 \text{nF}$$

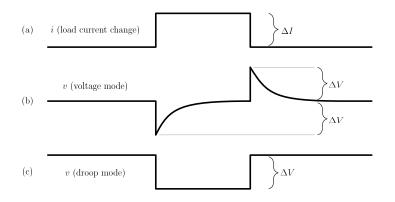

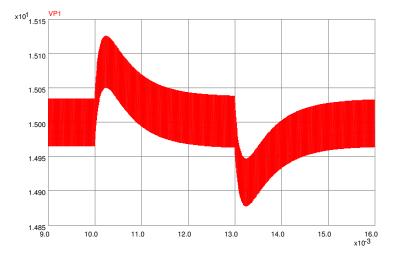

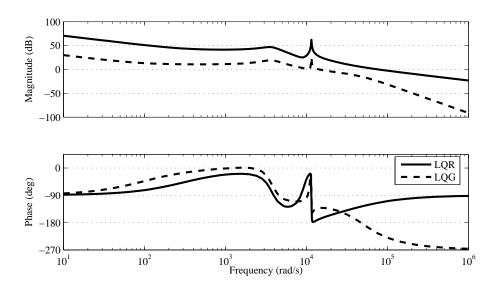

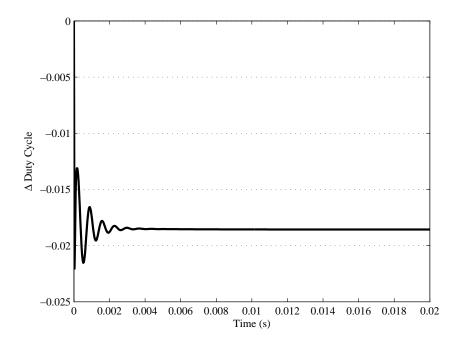

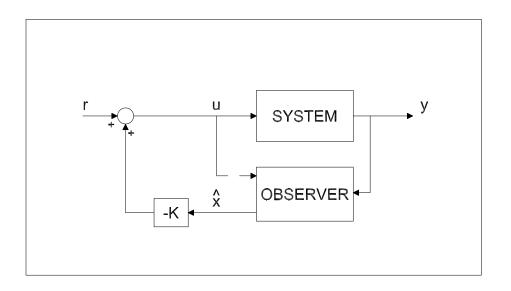

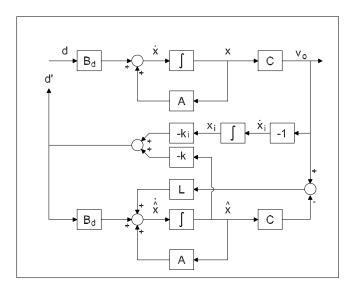

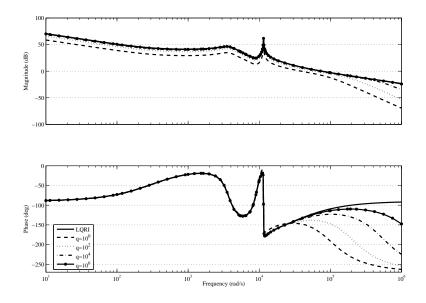

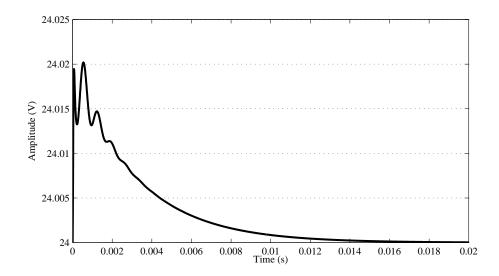

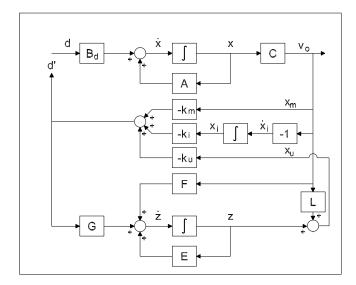

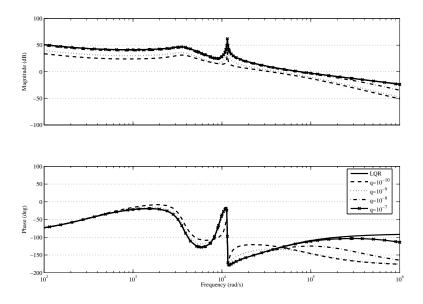

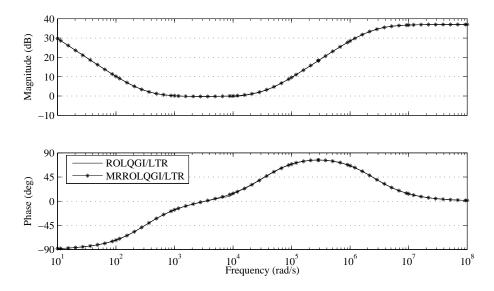

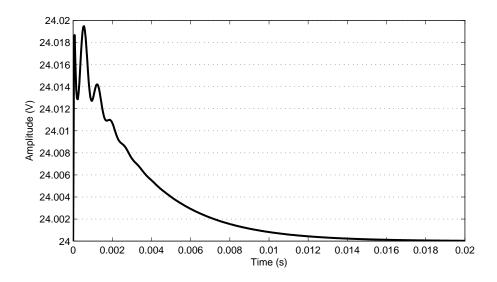

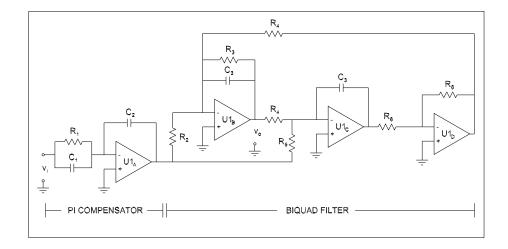

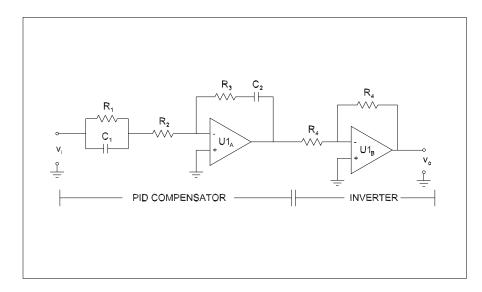

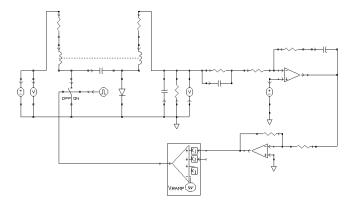

(4.20)